# Evolution of High-Speed Server and Computing Interfaces

Senior Project Manager / Keysight Technologies

Francis Liu & Jacky Yu

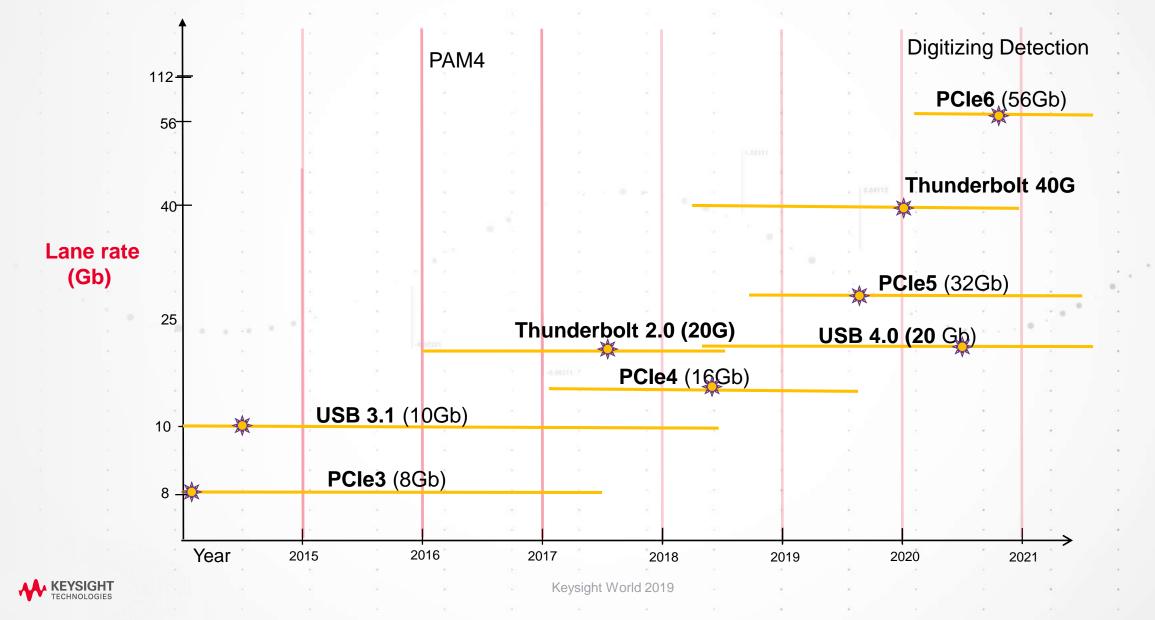

# **High-Speed Computing Roadmap**

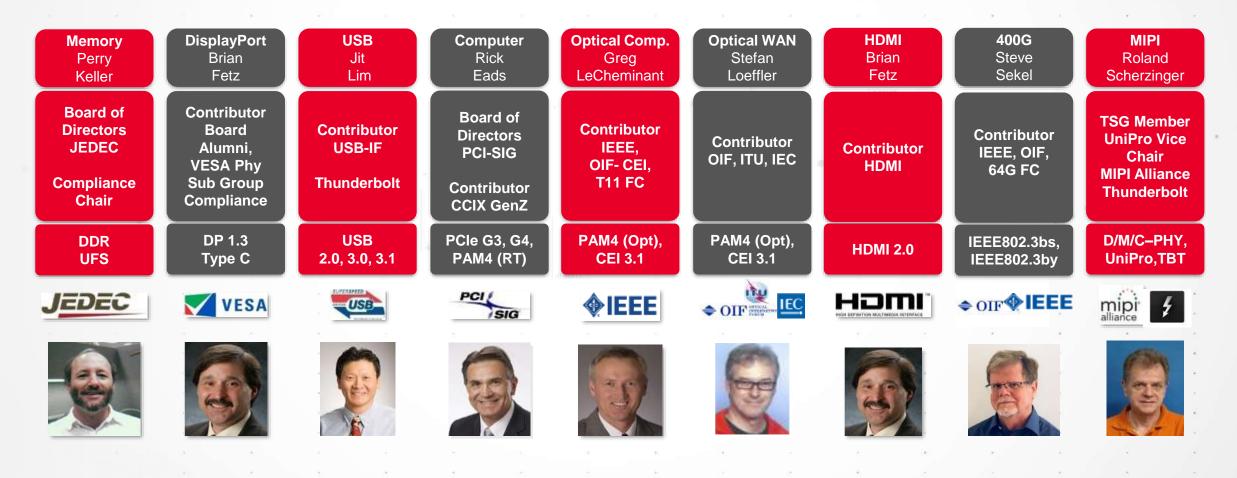

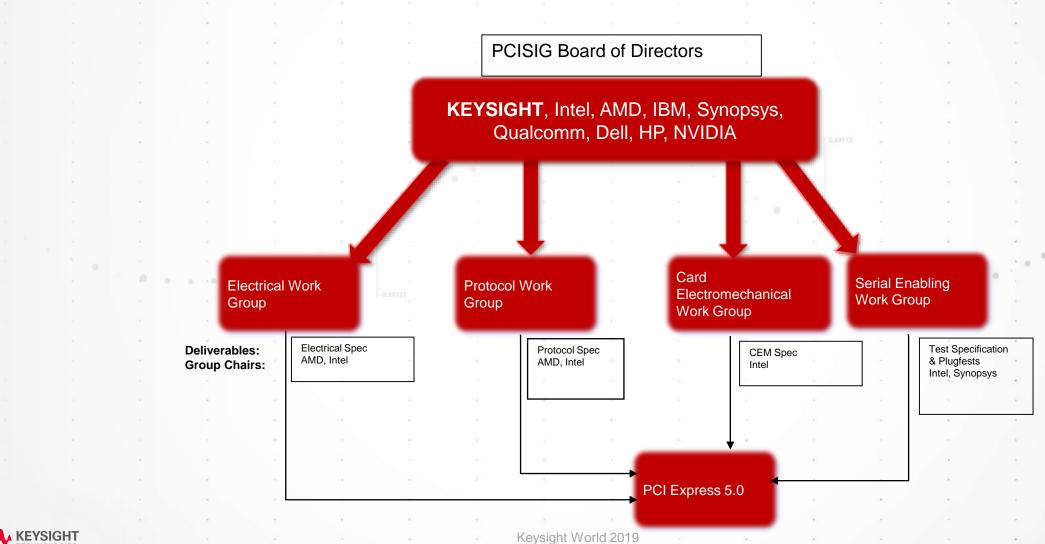

# **Keysight Participation in Standards**

### TRUST OUR EXPERTISE

KEYSIGHT TECHNOLOGIES

Keysight World 2019

# **Changes in High-Speed Digital Buses**

- DDR / LPDDR are moving to DDR / LPDDR5

- PCI Express (PCIe) is moving to PCIe Gen5

- Emergence of new computing standards (CCIX, GenZ, OpenCAPI, NVLink)

- Possible convergence of Type-C related buses

Keysight World 2019

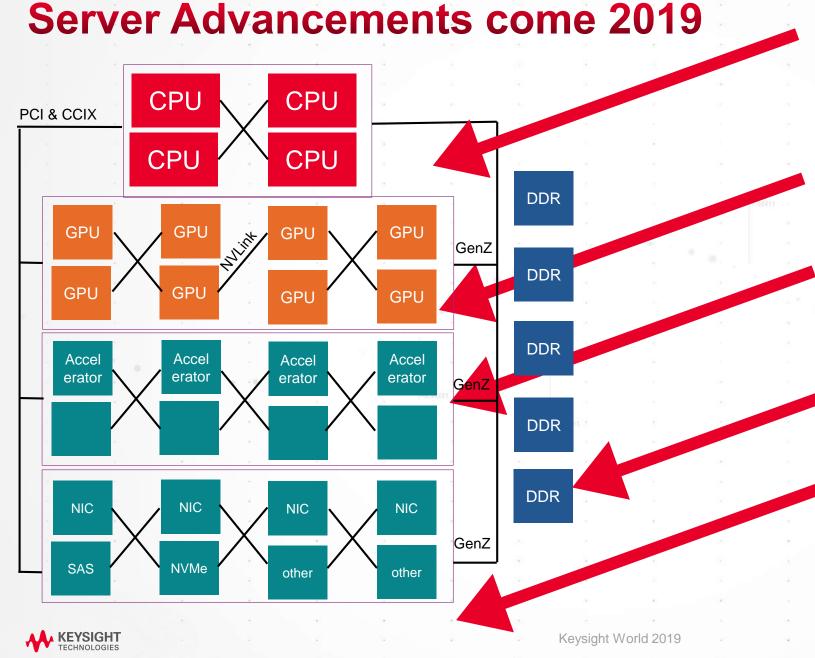

PCI Express / CCIX offer a choice to designers for CPU to accelerator communication

NVLINK replaces PCI Express for GPU to GPU communication running at >25 Gbps

PCI Express / GenZ battle for communications between memory and CPU

DDR4 is replaced by DDR5 for memory. LPDDR4 gives way to LPDDR5

OPENCAPI and other technologies push for the fabric of the server

Intel announces new CXL open bus for coherency

# PCI Express Gen5 – Moving to 32 Gbps

## **Drivers of PCIe 5.0 Performance**

- High end networking

- 400Gb Ethernet

- Dual 200Gb/s InfiniBand

- Storage Networking

- NVM Express (NVMe)

- Big Data

- Increased IC I/O Speeds

- Co-Processors (FPGA, GPU)

- ASIC

- IP

- Artificial Intelligence Engines

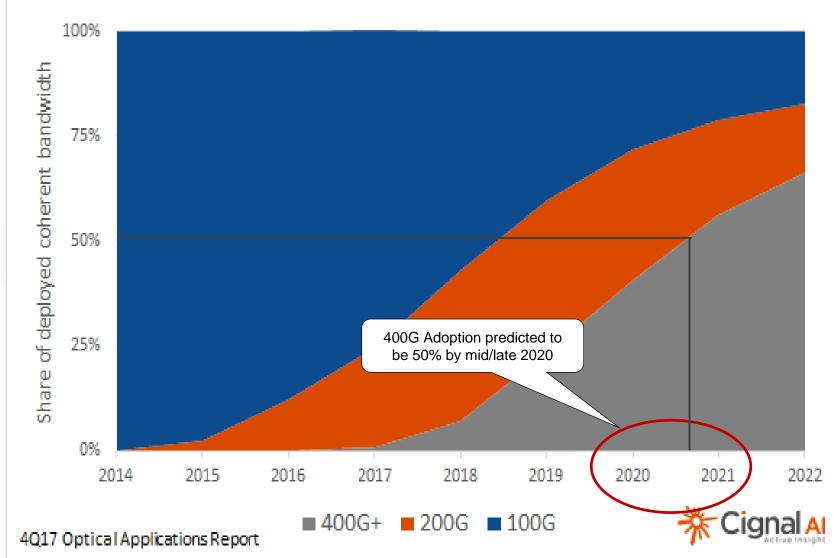

## Coherent Bandwidth by Speed

KEYSIGHT TECHNOLOGIES

# **Industry Drives Higher PCIe Bandwidth Requirements**

- PCIe 5.0 = 32 Gb/s

- Required for 400Gb Ethernet

- This equates to 50GB bidirectionally

- 16 lanes gives up to 64GB/s

- Total full duplex BW = 128 GB/s

- CEM connector for PCIe 5 is planned to be backward compatible with earlier PCIe technologies.

- Tentative schedule for spec release in 2019

|          |                      |         |       | 10  |                               |      |

|----------|----------------------|---------|-------|-----|-------------------------------|------|

|          | Raw Bit<br>Rate/Lane | Link BW | BW/La | ne  | Total x<br>Direction<br>Bandw | onal |

| PCIe 1.x | 2.5GT/s              | 2Gb/s   | 250 M | B/s | 8GB/s                         |      |

| PCIe 2.x | 5.0GT/s              | 4Gb/s   | 500 M | B/s | 16GB/                         | S    |

| PCIe 3.x | 8.0GT/s              | 8Gb/s   | ~1GB/ | 's  | ~32GE                         | 8/s  |

| PCle 4.x | 16.0GT/s             | 16Gb/s  | ~2GB/ | 's  | ~64GE                         | 8/s  |

| PCIe 5.x | 32.0GT/s             | 32 Gb/s | ~4GB/ | 's  | ~128 0                        | GB/s |

| 2 1      |                      |         |       |     |                               |      |

| a v      |                      |         |       | ÷   |                               |      |

| × *      |                      |         |       | *   |                               |      |

|          | 151 15               |         |       | 1   |                               |      |

|          |                      | ÷       | •     |     |                               | ÷    |

|          | 4                    |         |       |     | *                             | *    |

| .ee.     | 180 - A              |         |       | × . |                               | *    |

| 15 IS    | 1.5                  | 5 S     |       |     | 1                             | ÷    |

# **PCI Express Standards Development**

TECHNOLOGIES

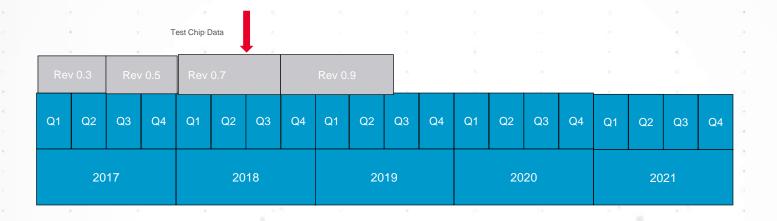

## **PCI Express 5.0 Timeline (estimated)**

- Draft 0.3 June 2017 🥥

- Draft 0.5 December 2017

- Draft 0.7 May 2017

- Draft 0.9 Stretch Goal end of 2018

- Final 1.0 "first half of 2019"

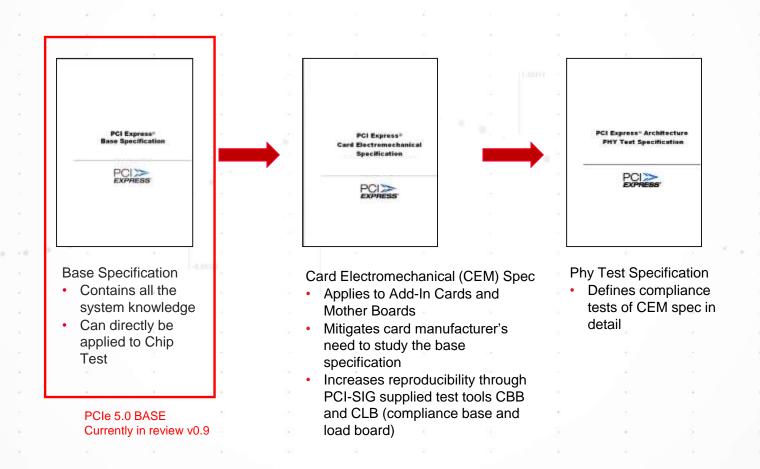

## **PCI Express Specifications and Scope**

## SELECT THE SPECIFICATIONS THAT RELATE TO YOUR NEED

-11

## PCIe Gen5

## GOALS

- BER target is 10e-12

- TX Presets P0-P10 to remain the same

- Backward compatibility with previous PCIe Gen1/2/3/4

- Same approach for TX and RX testing used for Gen4

- Similar method for TX testing via de-embedding of breakout board traces

- Similar method for calibrating the eye width and eye height as used with PCIe 4.0 (ISI based, fixed RJ)

- Same TX Voltage and Jitter parameters as Gen4

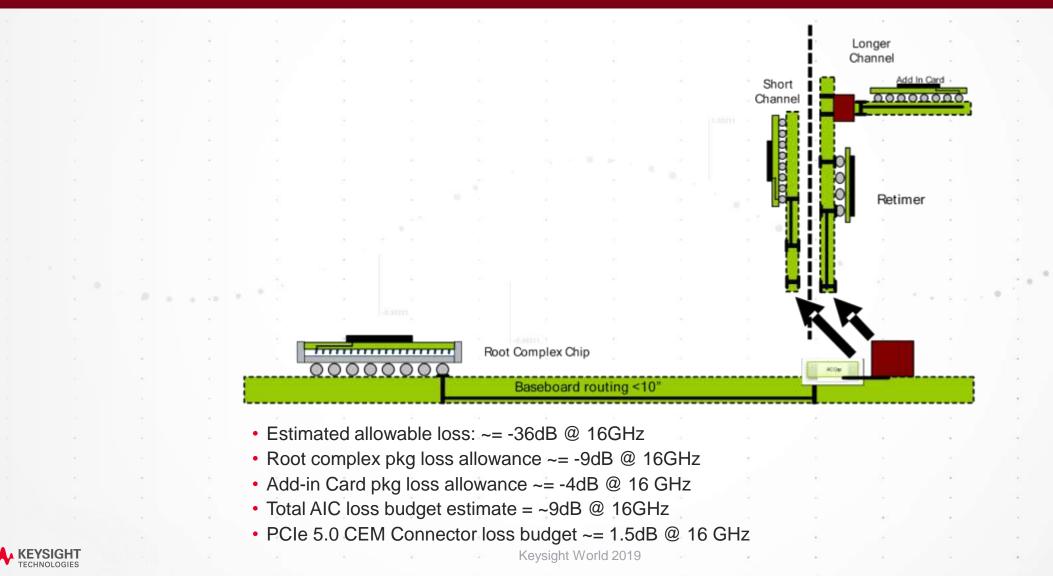

# **PCI Express 5.0 Channel Topology**

#### RETIMER REQUIRED WHEN LOSS EXCEEDS -36DB OR >1 CONNECTOR

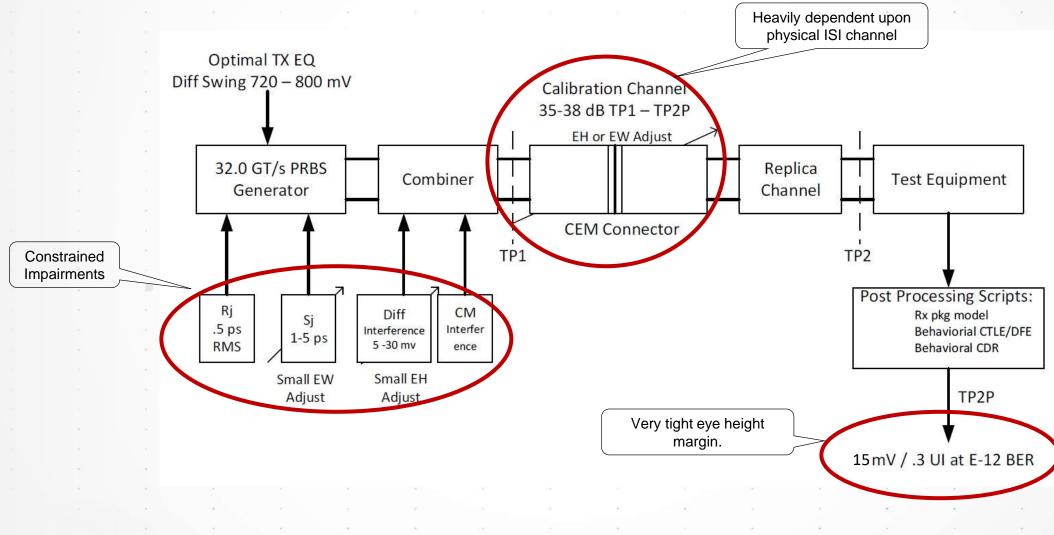

# PCIe 5.0 32GT/s RX Calibration (BASE)

## 15MV EYE HEIGHT POST EQ (0.3UI EYE WIDTH) TARGET

Keysight World 2019

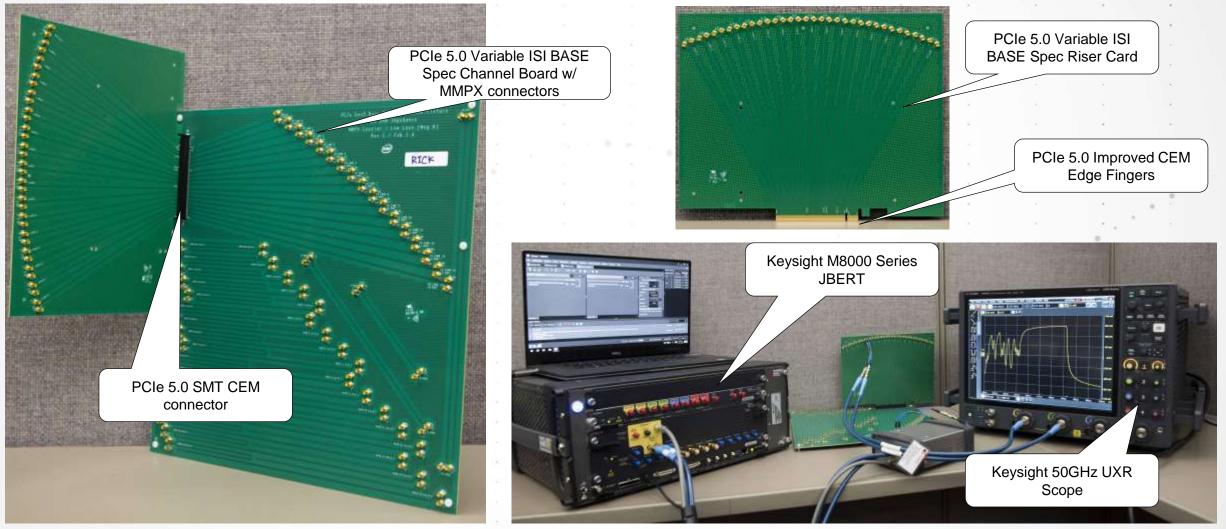

# PCIe 5.0 32GT/s RX Calibration (BASE) Example

## TARGET TEST CHANNEL BOARD W/ NEW CEM SMT CONNECTOR

# **D9050PCIC New Features**

### MASTER YOUR BEST DESIGN

- Supports PCIe 5.0 BASE TX Testing at 32GT/s as well as 2.5G, 5G, 8G and 16GT/s (v0.9 BASE)

- Supports PCIe 5.0 Reference Clock tests (2.5G, 5G, 8G, 16G)

- Will Support CEM tests for endpoints and root complexes (2.5G, 5G, 8G, 16G, 32G).

- Integrated De-embedding of break-out channel with optional InfiniiSim

- Automated DUT control using an 81150/60A Pulse Generator ARB.

- Enhanced Switch Matrix supporting arbitrary lane mapping

- Minimum oscilloscope BW: 50GHz

clude the additional signal distortion caused by the behavioral Receiver package. If a compliance pattern waveform is used then all stresses except  $V_{RX-CM-INT}$  are turned on if a step is used then all stresses are turned off. Then the resulting signal is recovered by means of Rx equalization, and a behavioral CDR function, resulting in an equivalent eye. The requirements for the waveform post processing tool used for the EH/EW calibration are described further in Section 8.4.2.1.1 Post Processing Tool Requirements .

As the calibration procedure of the signal generator output contains steps where the generator is connected directly to measurement instrumentation, the transition time of the output waveform can be very fast. Therefore, it is important that the bandwidth of instrumentation used to calibrate the generator be matched appropriately to the edge rate of the generator output. This specification requires the use of a generator for 16.0 GT/s testing whose outputs have a rise time of 14 ps-19 ps (20% / 80%) which also requires a minimum oscilloscope bandwidth of 25 GHz. This oscilloscope bandwidth is also the minimum required bandwidth for transmitter measurements at 16.0 GT/s. For 32.0 GT/s testing the specification requires the use of a generator whose outputs have a rise time of 7.5 - 15.0 ps (20%/80% measured with P4) which requires a minimum oscilloscope bandwidth of 50 GHz. This oscilloscope bandwidth is also the minimum required for transmitter measurements at 32.0 GT/s. A minimum oscilloscope sampling rate that captures at least 5 samples per unit interval is required for all data rates.

# Keysight D9050PCIC PCIe 5 (Gen5) TX Test Application

## 5.0 BASE SPEC TESTS

| Z PCI-Express Gen5 Test Application New Device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <u>File View Tools Help</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| Set Up Select Tests Configure Connect Run Automate Results HTML Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -            |

| <ul> <li>All PCI Express Gen 5 Tests</li> <li>32.0 GT/s Tests</li> <li>Transmitter (Tx) Tests</li> <li>Signal Quality</li> <li>Unit Interval</li> <li>Full swing Tx voltage with no TxEQ</li> <li>Uncorrelated total jitter</li> <li>Uncorrelated deterministic jitter</li> <li>Total uncorrelated PWJ</li> <li>Deterministic DjDD uncorrelated PWJ</li> <li>Pseudo package loss</li> <li>Data dependent jitter</li> <li>Random jitter</li> <li>Min swing during EIEOS for full swing</li> <li>Common Mode Voltage</li> <li>Y Tx, AC common mode voltage</li> <li>Tx, Absolute delta of DC common mode voltage</li> </ul> |              |

| (Click a test's name to see its description)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | × •          |

| Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| Summaries (click for details) Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 2019-01-09 10:06:00:460 PM Connected to Infinitum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ady for use. |

| 2019-01-09 10:06:02:142 PM Refreshing HTML Report<br>2019-01-09 10:06:02:186 PM HTML Report Refreshed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 2019-01-09 10:06:08:277 PM Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>v</b>     |

|                                                                                      |                                                                                              |                                                                                                                | *                                                                                                                                  | 5                | 8         |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|

|                                                                                      |                                                                                              |                                                                                                                | *                                                                                                                                  | 6                | 54<br>    |

|                                                                                      | . 0.64112                                                                                    | 3                                                                                                              |                                                                                                                                    |                  |           |

|                                                                                      | -                                                                                            |                                                                                                                |                                                                                                                                    |                  |           |

|                                                                                      | Overa                                                                                        | an Resi                                                                                                        | ult: PAS                                                                                                                           | 0                |           |

|                                                                                      |                                                                                              |                                                                                                                |                                                                                                                                    |                  | 1         |

|                                                                                      |                                                                                              | -                                                                                                              | ation Details                                                                                                                      |                  |           |

| Data Chann                                                                           | D                                                                                            | evice Des                                                                                                      | scription                                                                                                                          |                  |           |

| Data Chann                                                                           | D<br>1el +                                                                                   | evice Des<br>ChannelF                                                                                          | scription<br>R-1                                                                                                                   |                  |           |

| Data Chann                                                                           | D<br>nel +<br>nel -                                                                          | evice Des<br>ChannelF<br>ChannelF                                                                              | R-1<br>R-3                                                                                                                         |                  |           |

|                                                                                      | D<br>nel +<br>nel -<br>ne                                                                    | evice Des<br>ChannelF                                                                                          | R-1<br>R-3<br>rice1                                                                                                                |                  |           |

| Data Chann                                                                           | D<br>nel+<br>nel-<br>ne<br>Te                                                                | evice Des<br>ChannelF<br>ChannelF<br>New Dev                                                                   | scription<br>R-1<br>R-3<br>rice1<br>on Details                                                                                     |                  |           |

| Data Chann<br>Device Nan<br>Infiniium S                                              | D<br>nel+<br>nel-<br>ne<br>Te                                                                | ChannelF<br>ChannelF<br>ChannelF<br>New Dev<br>est Session<br>06.30.00                                         | Cription<br>-1<br>-3<br>rice1<br>on Details<br>701                                                                                 |                  |           |

| Data Chann<br>Device Nan<br>Infiniium S<br>Infiniium M                               | D<br>nel+<br>nel-<br>Te<br>W Version                                                         | evice Des<br>ChannelF<br>ChannelF<br>New Dev<br>st Session<br>06.30.00<br>DSAZ634                              | ecription<br>R-1<br>R-3<br>rice1<br>on Details<br>701<br>4A                                                                        |                  |           |

| Data Chann<br>Device Nan<br>Infiniium S<br>Infiniium M<br>Infiniium S                | D<br>nel +<br>ne<br>ne<br>Te<br>W Version<br>lodel Number                                    | evice Des<br>ChannelF<br>ChannelF<br>New Dev<br>st Session<br>06.30.00<br>DSAZ634<br>MY57220                   | Scription           R-1           R-3           rice1           on Details           701           4A           0110               |                  |           |

| Data Chann<br>Device Nan<br>Infiniium S<br>Infiniium M<br>Infiniium S                | D<br>nel +<br>ne<br>W Version<br>Iodel Number<br>erial Number<br>n SW Version                | evice Des<br>ChannelF<br>ChannelF<br>New Dev<br>st Session<br>06.30.00<br>DSAZ634<br>MY57220                   | Scription           R-1           R-3           rice1           on Details           701           4A           0110               |                  |           |

| Data Chann<br>Device Nan<br>Infiniium S<br>Infiniium M<br>Infiniium S<br>Application | D<br>nel +<br>ne<br>Te<br>W Version<br>lodel Number<br>erial Number<br>SW Version<br>de Used | evice Des<br>ChannelF<br>ChannelF<br>New Dev<br>st Session<br>06.30.00<br>DSAZ634<br>MY57220<br>0.99.902<br>No | Scription           R-1           R-3           rice1           on Details           701           4A           0110           9.0 | t Application (o | official) |

-17

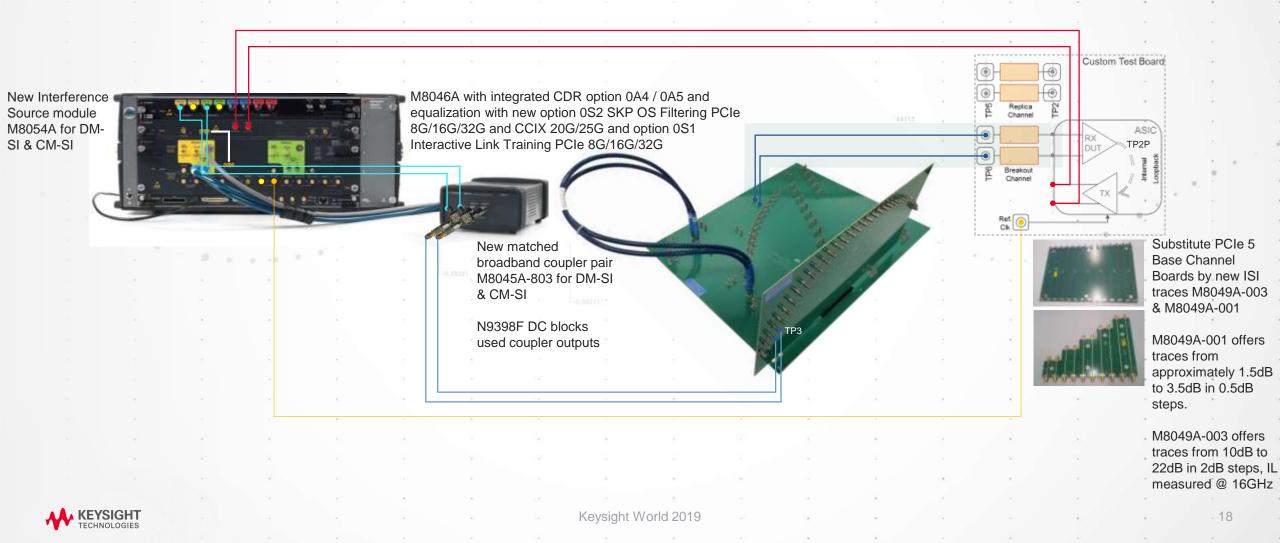

# PCIe 32G/16G/8G RX Test Setup

### SETUP USING M8000 SERIES 64G HIGH-PERFORMANCE BERT

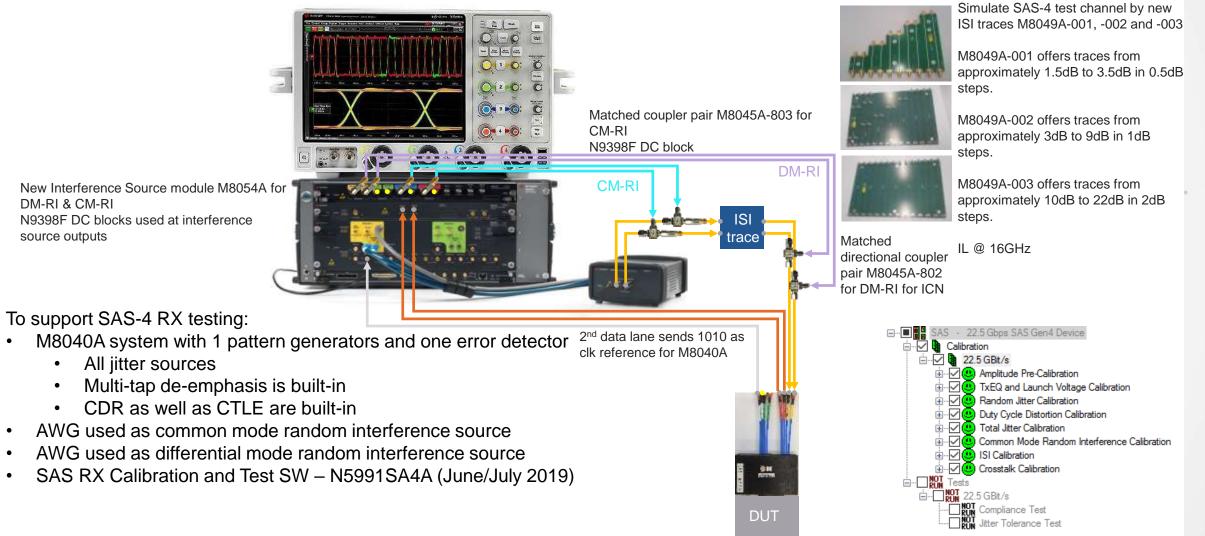

## SAS-4 RX Test Setup – Stressed RX Jitter Tolerance

### SETUP USING M8040A + M8054A INTERFERENCE SOURCE

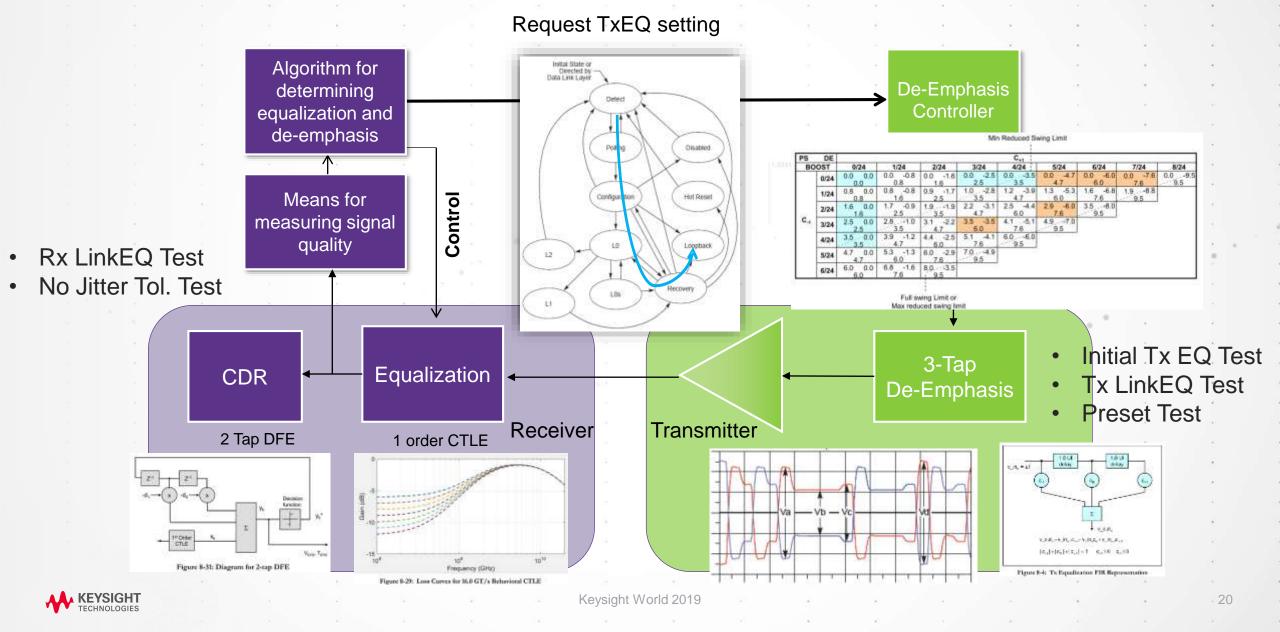

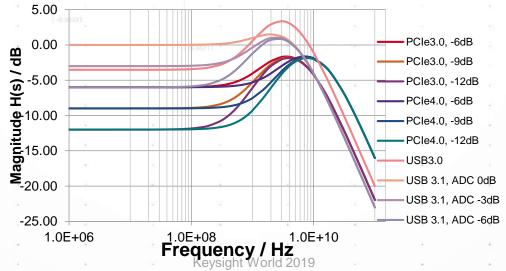

## **PCIe Tx EQ De-Emphasis and Rx Link Equalization**

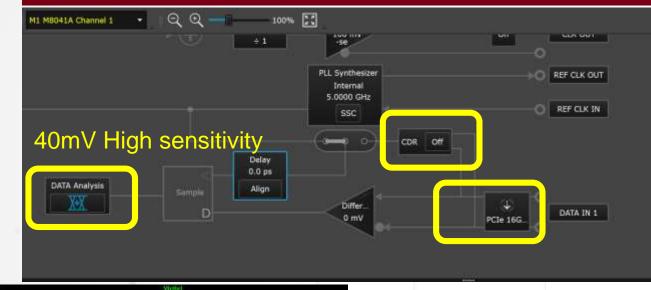

# Key of Successful PCIe Gen4 Rx testing: CTLE & CDR

Parameters

8 Y × 🛤

Input Timing

Equalization

Data rate

Equalization

pecific application

Selects input signal equalization for specific application The calibration of this parameter is only valid for the

INPut:EQUalization:PRESet 'M1.DataIn1',P6

Delay

M1.DataIn

0.0 ps -

PCIe 16Gb/s -9dB

### CHALLENGE IN CEM LONG TRACE

# The Key with Error Free:No additional loss with integrated CDR

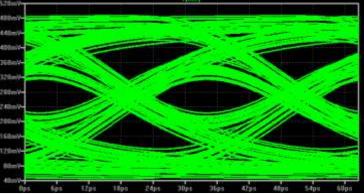

#### Tx signal after > 10 inches

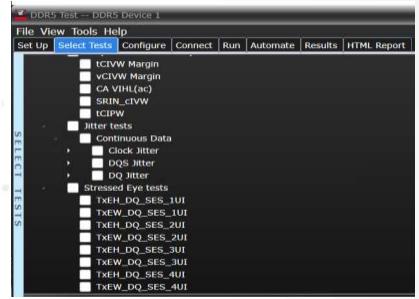

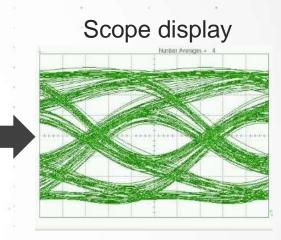

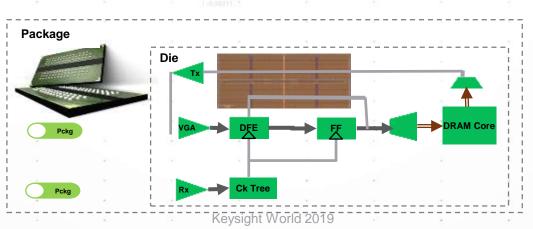

# DDR5 - Bring on Receiver Testing for DRAM

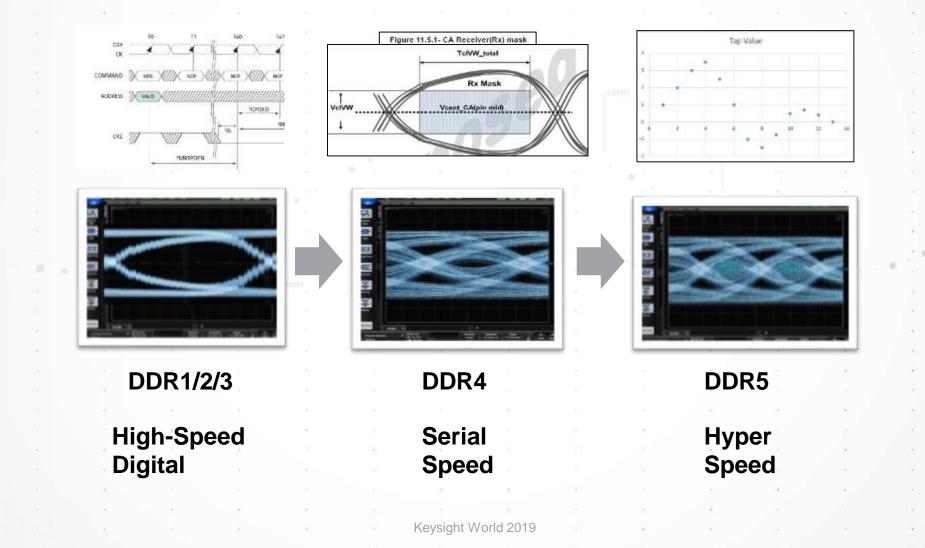

# **The New Age - DDR Signaling Evolution**

|                                                 |                                                                                                                          | Signai                     |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------|

| DDR6?                                           | <ul><li>"Light Speed"</li><li>Complex modulation?</li></ul>                                                              |                            |

| IQ Threshold<br>DDR5                            | <ul><li>"Hyper Speed" - No visible eye</li><li>Pre/De-Emphasis, Impulse response</li></ul>                               | 1.0243)                    |

| Impulse Response Threshold<br>DDR4              | <ul> <li>"Serial Speed" - Clock often embedded</li> <li>Eye Diagrams/Masks</li> <li>Error rates, Jitter/Noise</li> </ul> |                            |

| Jitter & Noise Threshold<br>DDR3<br>DDR2<br>DDR | <ul> <li>"High Speed" - Transmission lines</li> <li>Timing</li> <li>Impedance / load curves</li> </ul>                   | 1 0 1 0<br>0<br>Write<br>4 |

| Signal Integrity Threshold<br>Static RAM        | <ul> <li>"Low Speed" - Auto place and route</li> <li>Fanout</li> <li>Capacitance</li> </ul>                              | 18 20 3                    |

| KEYSIGHT<br>TECHNOLOGIES                        | Keysight World 2019                                                                                                      |                            |

Signal

## Just When You Thought it Was Safe...

## RULES ARE CHANGING WITH EVERY GENERATION- DDR5 IS COMING

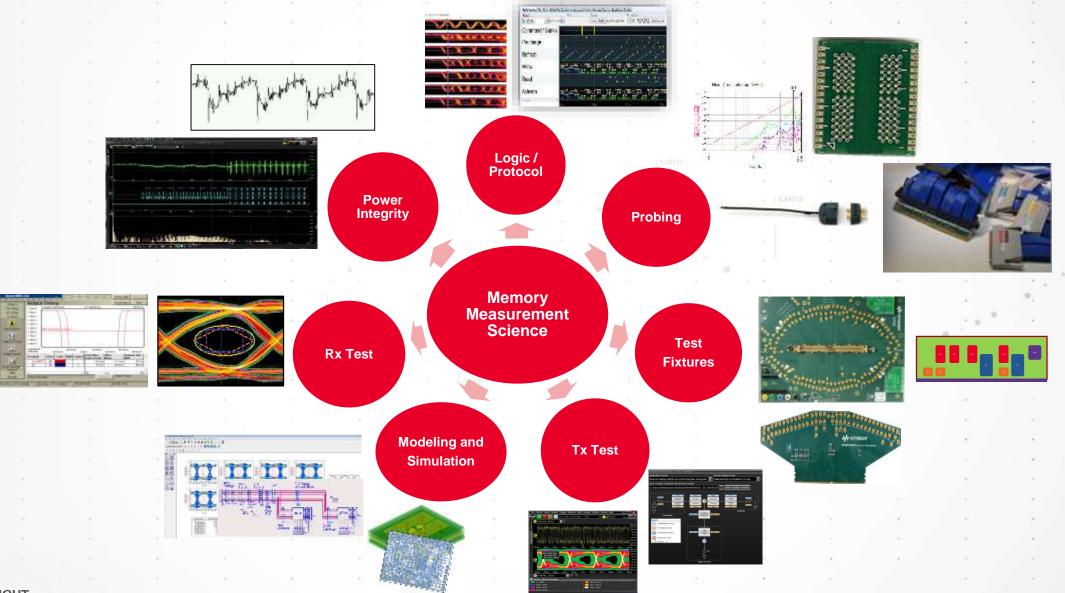

## **Measurement Science Domains**

KEYSIGHT

Keysight World 2019

## **DDR5 Specification and Measurement**

KEYSIGHT TECHNOLOGIES

Keysight World 2019

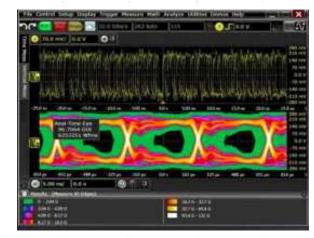

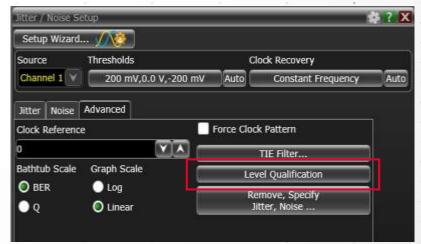

# **New Tx Measurement Science**

### Characterization of CLK, DQS, DQ

- Mismatch between DQS and DQ (tDQS2DQ)

- Rj/Dj jitter separation to allow designer to identify design issues

- Rj source of noise

- Dj source of crosstalk and duty cycle distortion

#### • DQ stressed eye test

- Eye height and eye width measurement

- DFE for higher data rates

- Account for instrument noise

Keysight World 2019

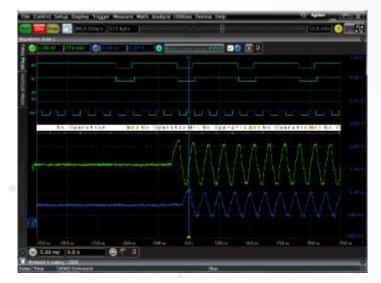

## **New Read/Write Separation Method**

Command protocol decode with mixed signal oscilloscopes

- Use command truth table to decode read and write commands

- Pros: More robust

- Cons: Requires additional signals. More signals -> More loading

#### Read or write only control

• System designer has control over data transition type through SOC, FPGA.

Kevsial

- Pros: Eliminates the need for read/write separation

- Cons: Not an option for system integrators

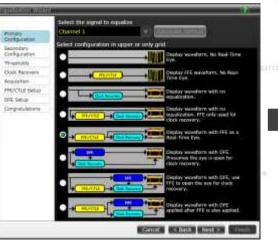

# **De-embedding and Equalization**

## VIRTUAL PROBING METHOD AT RX EQ

## Package Model

## Rx Model

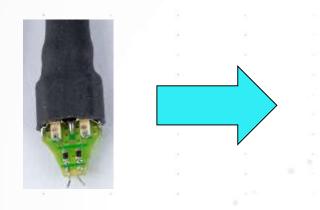

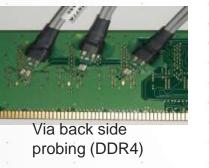

# **Probing Technology**

Higher speeds require smaller, higher density probing with lower loading

KEYSIGHT TECHNOLOGIES

Reduced loading **DIMM** interposer for logic analysis

BGA interposer

Detailed simulation modeling correlated to physical prototypes

# **DDR/PCI Express Comparison**

## • Full rate clock

No Rx PLL needed

## Wide, single ended

- Xtalk dominated vs. loss dominated

- Increased emphasis on multi-channel Rx test impairments

## Bidirectional

- Extra parasitic loading when Rx and Tx share pins

- There is no clean way to terminate the bus

- Reflections due to ODT changes, adjacent rd/wr bursts

## Bursty

• ISI impact differs on preamble, first bits, rest of burst

## <u>Rx must work using "slow" DRAM process</u>

- Full rate loopback impossible

- "Dumber" Rx increases test complexity

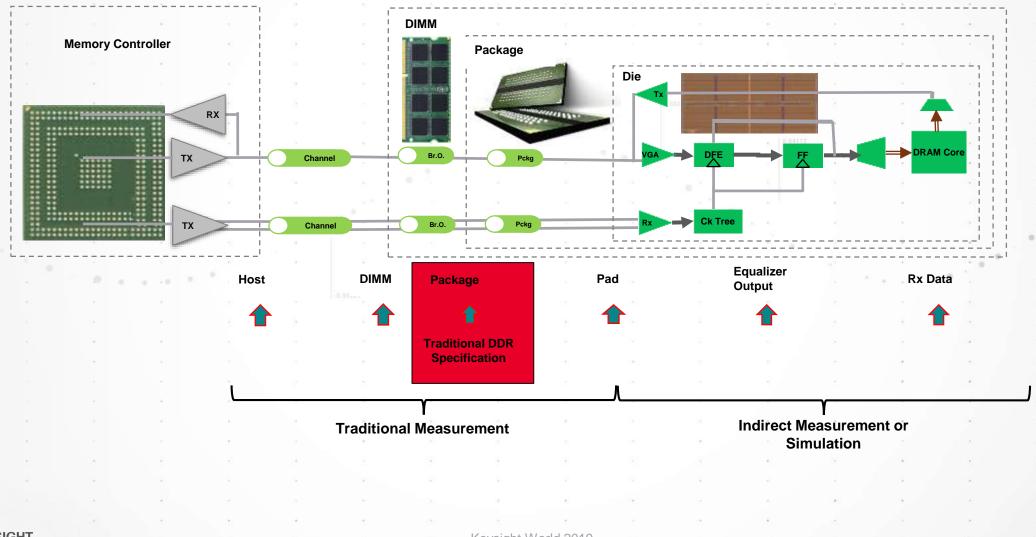

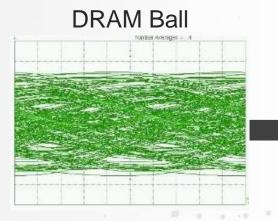

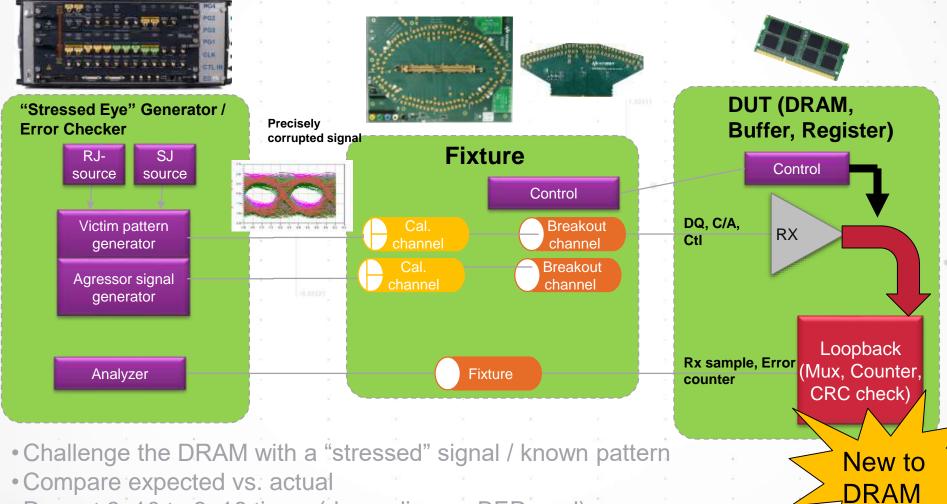

# **Receiver Testing Begins in DRAM**

## **RX TESTING AND EQUALIZATION**

Keysight World 2019

• Repeat 3e10 to 3e16 times (depending on BER goal)

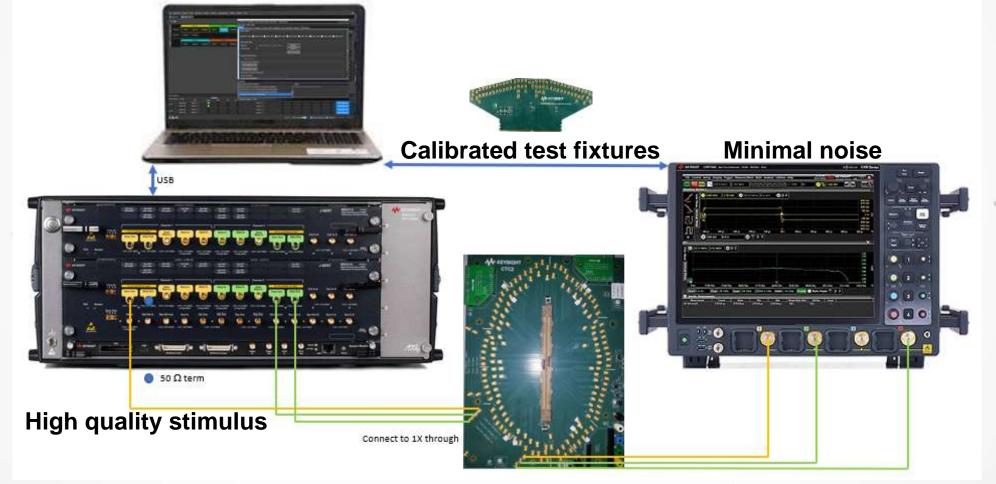

# **Receiving Testing Needs**

### CREATE A WELL CONTROLLED TEST SETUP

### **Repeatable procedures**

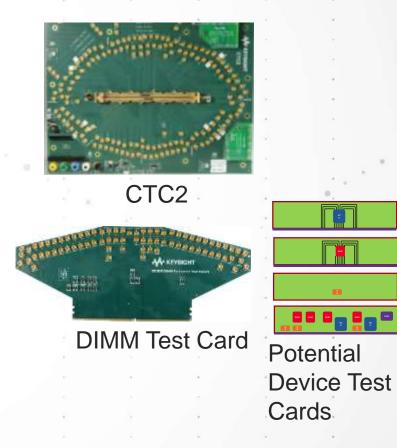

## **Device and System Testing Fixture**

AUTOMATED DEVICE CHARACTERIZATION AND GOLDEN CHANNEL

Channel Test Card "CTC2"

Socket for plugging in DIMM test card for calibration, DIMM module to be tested or device test board. SMP connectors to provide access to CA/CTRL, strobe, and data

- Golden Channel Modeling Board (or ISI Board)

Contains different length standard compliant channels

- Device Test Card

Plugs into CTC and can be used by DRAM/memory/register manufacturers to test their chips

Fully Passive DIMM Test Card

Plugs into CTC. Signal breakout board for clock, CA, CTRL, strobe and data. Used for signal inspection and Rx stress signal calibration. Signals are routed to SMP connectors.