# 400G: Looking Forward to 800G and Terabit Speeds

Senior Project Manager / Keysight Technologies

Joe Lin

### Agenda

- Introduction

- PAM4 Simulation

- 400G -> 800G Measurements

- Direct Detect Output (Transmitter) Test

- Direct Detect Input (Receiver) Test

- Coherent Optical Test

- Layer 2-3 Analysis

- Summary

### **Wireline Internet Infrastructure**

### Why Does the Industry Need PAM4?

#### ENABLES HIGHER DATA THROUGHPUT

- NRZ > 28 Gb/s limits trace length or increases cost

- PAM4 yields 2 bits / symbol

- Effectively halves the channel BW needs

- Allows designers to develop products to fit the cost structure of available channel technologies.

- PAM4: Pulse Amplitude Modulation 4-level

- 2 bits of information in every symbol

- 2x throughput for the same baud rate

- ✓ 26.56 Gbaud PAM4 = 53.125 Gb/s

- Lower SNR, more susceptible to noise

- More complex Tx/Rx design, higher cost

Figure 5: CEI-56G VSR NRZ channel

KEYSIGHT TECHNOLOGIES

Keysight World

### State of the '400G Class' Standards

#### CURRENT GENERATION - 50G LANE RATE

|              | •   | OIF-CEI-56G                                             |                | Released                      |

|--------------|-----|---------------------------------------------------------|----------------|-------------------------------|

| 2            |     | 5 reaches PAM4 up to 29 Gbaud, NRZ up to 58 Gb/s        |                |                               |

| 1            | •   | IEEE 802.3bs 200/400G (Ethernet)                        |                | Released                      |

|              |     | Medium reach SMF + C2C,C2M, PAM4 @ 53.1 & 26.6 Gbaud    |                |                               |

| $\checkmark$ | •   | IEEE 802.3cd: 50/100/200G (Ethernet)                    |                | Released                      |

|              |     | Short reach MMF. + C2C,C2M, backplanes & cables, PAM4 @ | 26.6 Gbaud     |                               |

|              | •   | 64G Fibre Channel                                       |                | Complete, pending publication |

|              |     | 100m – 2 km reaches in MMF & SMF, PAM4 @ 28.9 Gbaud     |                |                               |

| 1            | . • | COBO version 1.0                                        |                | Released                      |

|              |     | (Optical PHY from 802.3bs, Elec. from OIF-CEI-56G-VSR)  |                |                               |

|              | •   | IEEE 802.3cm 400G                                       |                | Under development             |

|              |     | Short reach in MMF, PAM4 @ 26.6 Gbaud                   |                |                               |

|              | •   | IEEE 802.3cn 50/100/200/400G                            | ан а<br>1960 а | Under development             |

|              |     | 10 km SMF, PAM4                                         | 92 - P         |                               |

|              | •   | OIF 400ZR                                               | ж. ж.          | Under development             |

|              |     | 80 km SMF, DP-16QAM @ 60 Gbaud, coherent                | 10 K           |                               |

|              | •   | IEEE 802.3ct 100/400GBaseZR                             |                | Under development             |

|              |     | 80 km SMF, DP-16QAM, coherent, (based on OIF 400ZR)     | ж) —           |                               |

| KEY          | SIG | T<br>Es                                                 | а<br>А         |                               |

### **Next-Generation '800G Class' Standards**

#### **112G LANE RATES**

- OIF CEI-112G

5 reaches PAM4, CNRZ-5

- IEEE 802.3ck

C2M & C2C for 2<sup>nd</sup> wave 400GbE & 800G

- Fibre Channel PI-8 128GFC Moving closer to Ethernet baud rate

Project starts for 5 reaches, C2M at 7<sup>th</sup> draft

First baseline draft for C2M May2019 (based on OIF CEI-112G-VSR, MR, and LR)

Project Start

1-2.50221

### Is 800G Really Starting Yet?

- First equipment using 400G is close to deployment

- Few remaining initial wave of '400G class' standards finishing up

- No 802.3 official study groups started for first 800G optical links yet

- Electrical chip-to-module, chip-to-chip, and backplane interface projects have started supporting >112 Gb/s per lane

### **Thoughts / Assumptions 800G Enabling Technologies**

- Optical 56 Gbaud PAM4 Proven in 400GBASE-DR4 (part of 802.3bs)

- Electrical mostly 56 Gbaud PAM4

- Most (but not all) detectors will digitize with DSP

- Optical and electrical links continue to rely on FEC to restore error free link

- FEC will pass through and not processed in module

- Will there be a 224G C2M AUI?

- Not without higher bit/symbol modulation. Some multi-wire modulations are being studied.

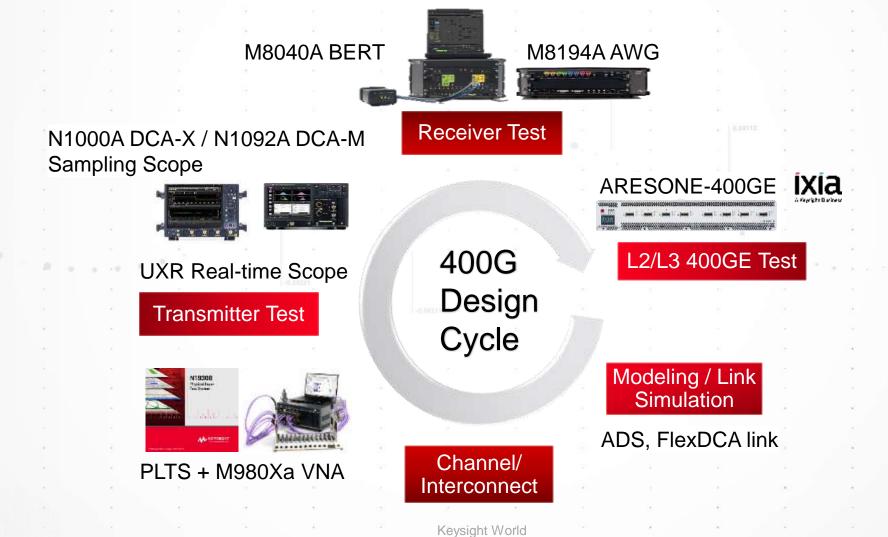

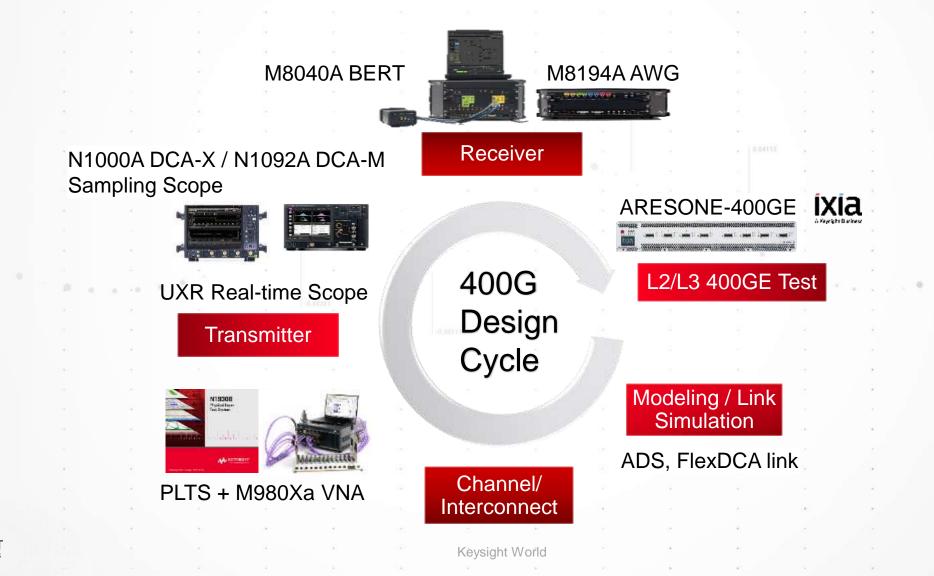

### **400G Solution Overview**

#### **END-TO-END SOLUTIONS FROM KEYSIGHT**

**KEYSIGHT** TECHNOLOGIES

- 9

# **PAM4** Simulation

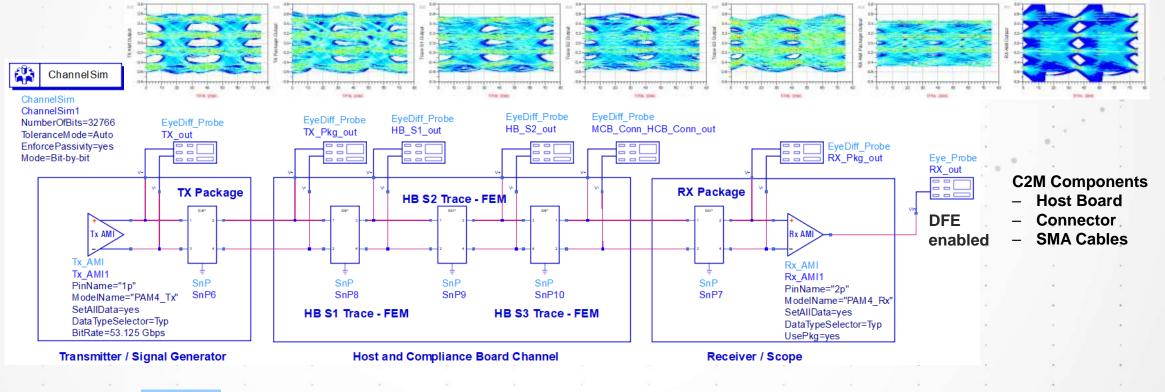

### **PAM4 Channel Simulation with AMI Model**

#### EXAMPLE: 400G CHIP-TO-CHIP (C2C) TEST BENCH SETUP

Keysight ADS SW provides comprehensive PAM4 Channel Simulation Analysis using vendor IBIS-AMI models

Test Setup: TP0 to TP5 (ball-to-ball)

**KEYSIGH**

http://www.eda.org/ibis/

Keysight World

IBIS (<u>IO Buffer Info Specification</u>) AMI (<u>Algorithmic Modeling Interface</u>)

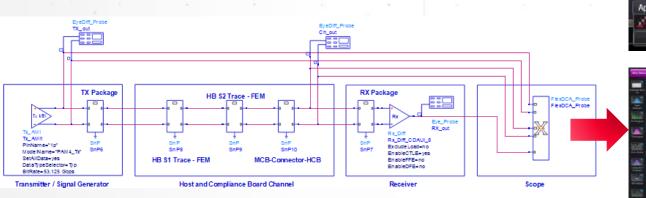

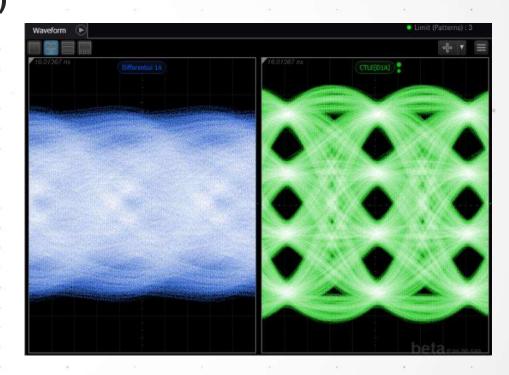

### **Correlate PAM4 Simulations with Measurement**

#### ADS 2019 TO FLEXDCA "CONNECTED FLOW"

- Connects simulation and measurement domains seamlessly: <u>"Design to Test"</u>

- Uses the same measurement algorithm and methodology on both simulated and measured waveforms

- Expands ADS PAM4 measurement capabilities to include <u>Jitter analysis and TDECQ</u>

- Runs <u>compliance apps</u> on simulated and measured waveforms

#### ADS Simulation Domain

#### Compliance Apps

FlexDCA – Eye/Jitter Analysis

#### Transmitter compliance measured at TPO

#### DCA-X Oscilloscope Measurement Domain

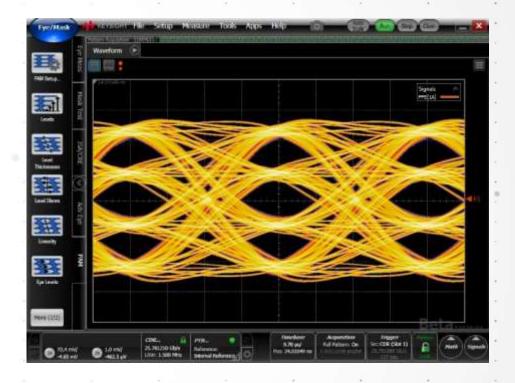

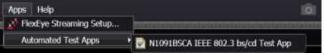

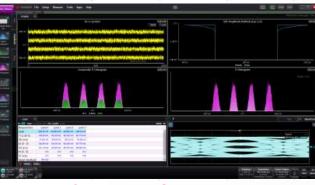

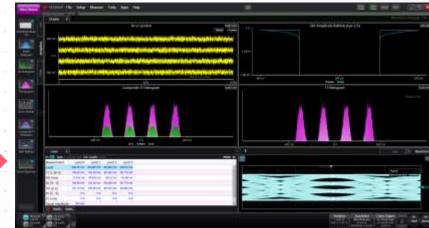

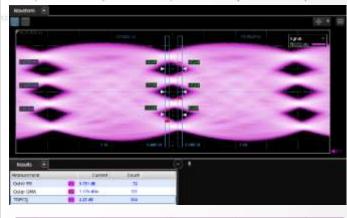

### PAM4 Analysis using ADS 2019 and FlexDCA

#### PAM4, JITTER, COMPLIANCE APPS

- ADS starts FlexDCA automatically

- Unlock all built-in comprehensive PAM4 analysis in FlexDCA

- o Eye contour

- TDECQ (Transmitter Dispersion Eye Closure Quaternary)

- Outer OMA

- o Linearity

- Noise Margin

- Partial SER

- Partial TDECQ

- Levels, Level Skews

- Eye Skews, Height, and Width..

- Jitter Analysis

- Run Compliance Apps

| Apps Help               |                                         | iâ |

|-------------------------|-----------------------------------------|----|

| FlexEye Streaming Setup | nosannnasannasannasa                    |    |

| Automated Test Apps     | Y 🛃 N10918SCA IEEE 802.3 bs/cd Test App |    |

#### Math and DSP in FlexDCA

Keysight World

#### ADS Waveforms -> FlexDCA

#### **Jitter Analysis**

# Direct Detect Output (Transmitter) Test

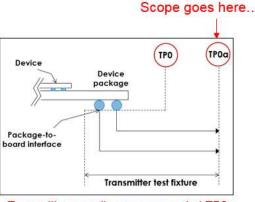

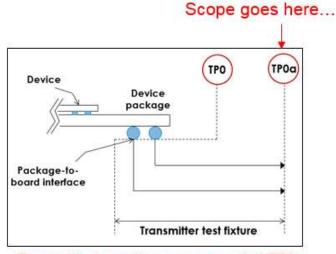

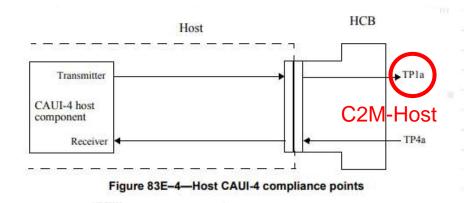

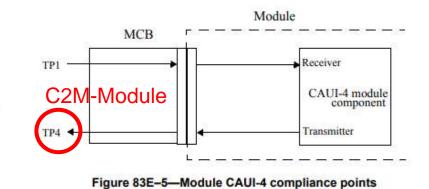

### Where Do the Tx Parameters Get Tested?

#### IEEE 802.3BS ELECTRICAL TX TEST POINTS

Transmitter compliance measured at TP0a

#### Chip-to-Chip (C2C) at TP0a (custom fixture)

Chip-To-Module (C2M) at TP1a (use compliant fixture)

Chip-to-Module Module Output (C2M) at TP4 (use compliant fixture)

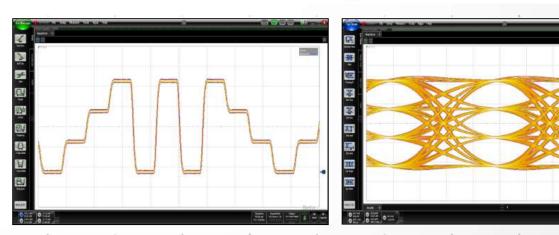

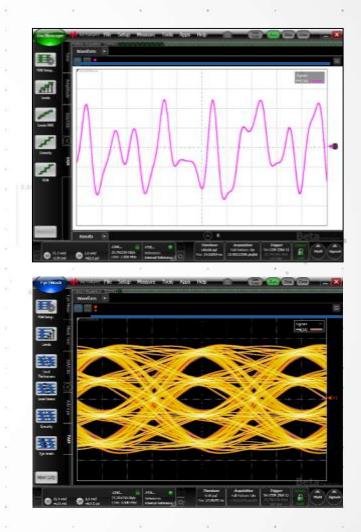

### **Measurement Challenges for PAM4 Test**

#### NEW ANALYSIS METHODOLOGY REQUIRED TO ANALYZE DEGRADED SIGNALS

#### Baud rates continue to increase (from 26 to 53 Gbaud)

• Standards (IEEE 802.3bs/cd, CEI 4.0,...) require:

- higher bandwidth test equipment

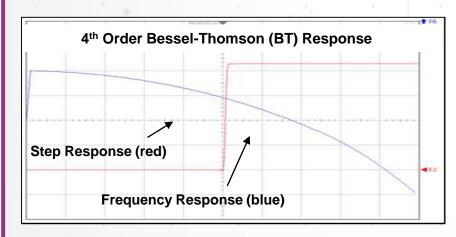

- ✓ "ideal" 4th Order Bessel-Thomson reference receiver response

- equalization to open signals for analysis

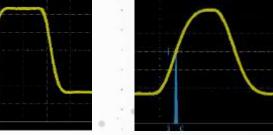

#### Degraded PAM4 Eyes

Requires low noise reference receivers and advanced clock recovery

- Complex New Measurements

- o Requires advanced analysis tools

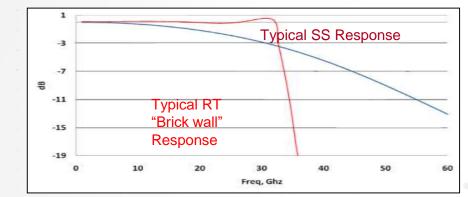

### **Compliant Frequency Response (Reference Receiver)**

#### **Receiver Frequency Response:**

Scopes have different frequency responses:

- Will result in different eye/waveform shapes and amplitudes

–> different measurement results

- To achieve 33/40 GHz 4<sup>th</sup> Order BT response on a RT scope, must start with > 60 GHz "brick wall" response

To provide more measurement consistency, most standards now specify BW and shape.

Examples (26 Gbaud PAM4; 53 Gb/s):

• IEEE 802.3bs™/D3.5 (Ethernet)

Clause 120D.3.1 200GAUI-4 or 400GAUI-8 transmitter characteristics: "A test system with a fourth-order Bessel-Thomson low-pass response with 33 GHz 3 dB bandwidth is to be used for all transmitter signal measurements, unless otherwise specified."

#### • CEI-56G-VSR-PAM4

#### Section 16.3.4 Output Differential Voltage, pk-pk

"The waveform is observed through a fourth-order Bessel-Thomson response with a 3-dB bandwidth of 40 GHz using a QPRBS13-CEI pattern."

### Bandwidth for "112G" (56 GBd)

#### PROPOSED 43 GHZ BESSEL

- 43 GHz Bessel response is deemed to be representative of "112G" transmitters (chip -> package -> fixture)

- Will this be sufficient BW for Tx characterization? Will 43 GHz BW penalize (reduce EH/EH margins) designs with better SI performance?

### **Clock Recovery for PAM4 Designs**

#### **Clock recovery (CR)**

- Recovers a clock for the Rx to use in real systems

- Scopes need to emulate CR used in real Rx (track out low-frequency jitter, trigger the scope)

#### **PAM4 adds complexity**

- Transitions no longer only at 0V diff

- CR Loop BW reduced from 10 MHz to ~ 4 MHz (IEEE 802.3bs/cd and CEI-56G-PAM4, same for 112G standards)

#### Instrument clock recovery

- Real-time oscilloscopes use software CR

- Equivalent-time oscilloscopes (aka Sampling scopes) use hardware CR

- CR needs to be able to lock onto "closed eyes"

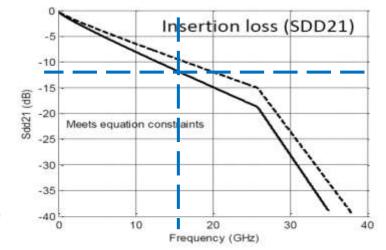

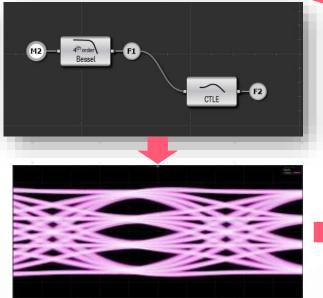

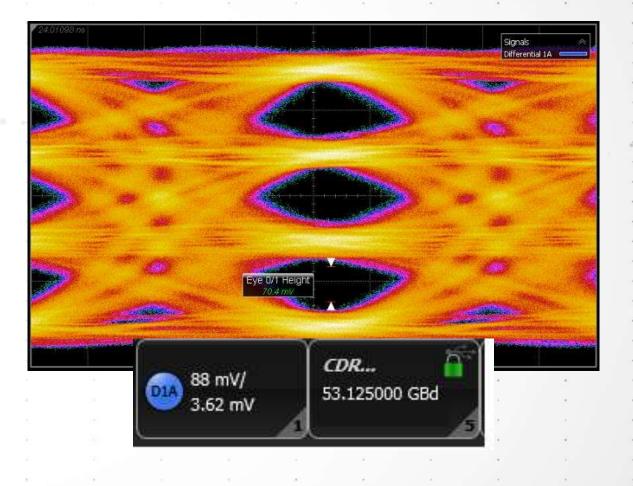

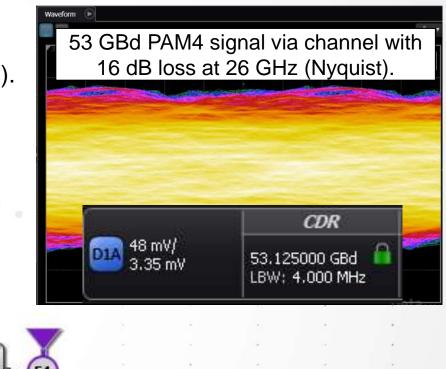

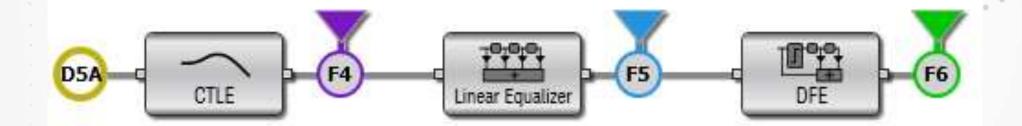

### Analyzing Degraded PAM4 Signals at 53 Gbaud (112G)

#### HIGHER CHANNEL LOSS, XTALK, AND REFLECTIONS AT 53 GBAUD (106 GB/S)

**C2M Channel Insertion Loss (IL):** Up to 16dB at 26.56 GHz (proposed). Whole link insertion loss can be more than 20dB.

Step 1: Scope must obtain CR lock (SW or HW) in order to analyze/equalize signals

Ensure the CR in your instrument can lock onto severely closed eyes

**Step 2: Equalize the signal and analyze**

• **"56G" Today:** only uses CTLE (up to 9 dB)

• **"112G" Future:** will likely require a combination of CTLE, FFE (5 tap?, 12 tap?), and/or DFE

(F5

D5/

CTLE

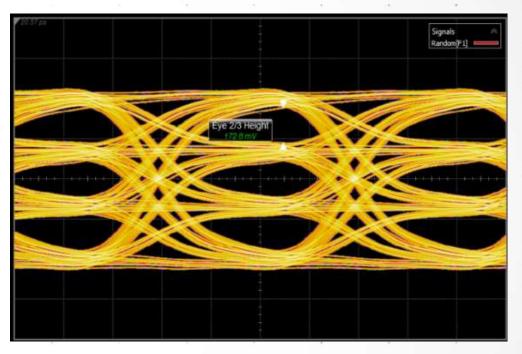

### Which Tx parameters Get Tested?

#### **KEY PAM4 MEASUREMENTS FOR ELECTRICAL TRANSMITTERS**

- Eye Width (EW), Eye Height (EH)

- Eye Symmetry Mask Width (ESMW)

- Output waveform

Level Separation Mismatch Ratio

- Signal-to-noise-and-distortion ratio (SNDR)

- Output jitter

J<sub>RMS</sub>

J3u, J4u

Even-Odd Jitter (EOJ)

While these parameters may sound familiar to you, they are measured very differently compared to legacy NRZ designs

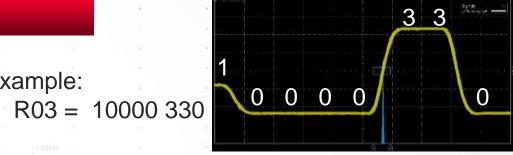

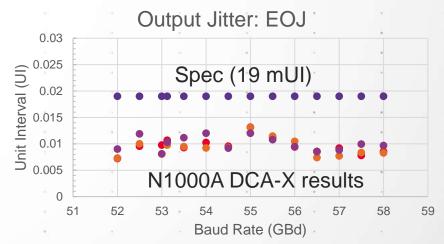

### **Output Jitter: Characterize 12-Edges of a PRBS13Q Pattern**

Example:

#### MEASURE J3U, J4U, J-RMS, EVEN-ODD JITTER

- Output Jitter parameters for Tx:

- o J3u (e.g. IEEE 802.3cd)

- o J4u (e.g. IEEE 802.3bs and CEI-56G-MR/LR)

- J<sub>RMS</sub> 0

- Even-Odd Jitter (EOJ)

- Measured on 12 specific transitions of a PRBS13Q (IEEE) and QPRBS13-CEI pattern (8191 symbols long) in order to exclude correlated jitter

- 12 transitions represent all possible combinations of 4 identical symbols followed by 2 different identical symbols

- Captures any jitter issues in Tx design

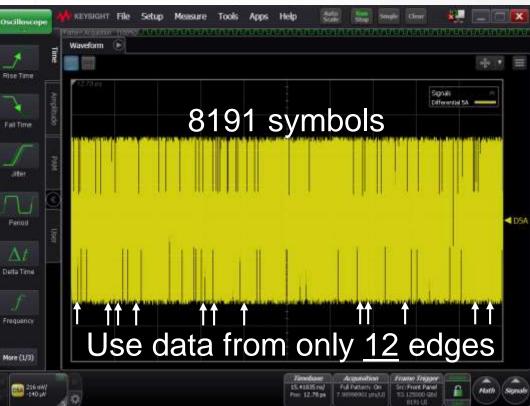

### **Measurement Considerations/Tips: 12-Edge Output Jitter**

#### SPEED AND REPEATABILITY

- Output Jitter (J3u, J4u, J<sub>RMS</sub>, and EOJ) can be a very time consuming measurement

- o Requires optimized algorithms

#### Requires a very stable and repeatable timebase

Check for scope repeatability (figure of merit: StdDev)

#### AM-to-PM conversion will impact results

Random noise (RN) will increase measured jitter as channel loss increases (edges will slow down).

• Expect an increase in J4u, JRMS as channel loss increases.

### How much data is required for an "accurate" measurement?

RJ/PJ histogram of > 400k typically samples yields stable results

Higher channel loss and crosstalk will necessitate more data

| Src: DIA Rate: 26. | Estimate Data Long   |

|--------------------|----------------------|

|                    | 562533 GBd Pat. Leng |

| Measurement        | Current              |

| 🕀 J4u (All)        | 1.6 ps               |

| 🕣 Jrms (All)       | 240 fs               |

| 🕀 EOJ (All)        | 450 fs               |

### Infiniium UXR-Series Real-Time Oscilloscope and N1000A DCA-X Oscilloscope

#### ENGINEERED FOR TESTING 400G/800G DESIGNS ... AND BEYOND

UXR-Series Real-Time Oscilloscope

#### N1000A DCA-X Equivalent-Time "Sampling" Oscilloscope N1060A Precision Waveform Analyzer (aka "MegaModule")

Keysight Worl

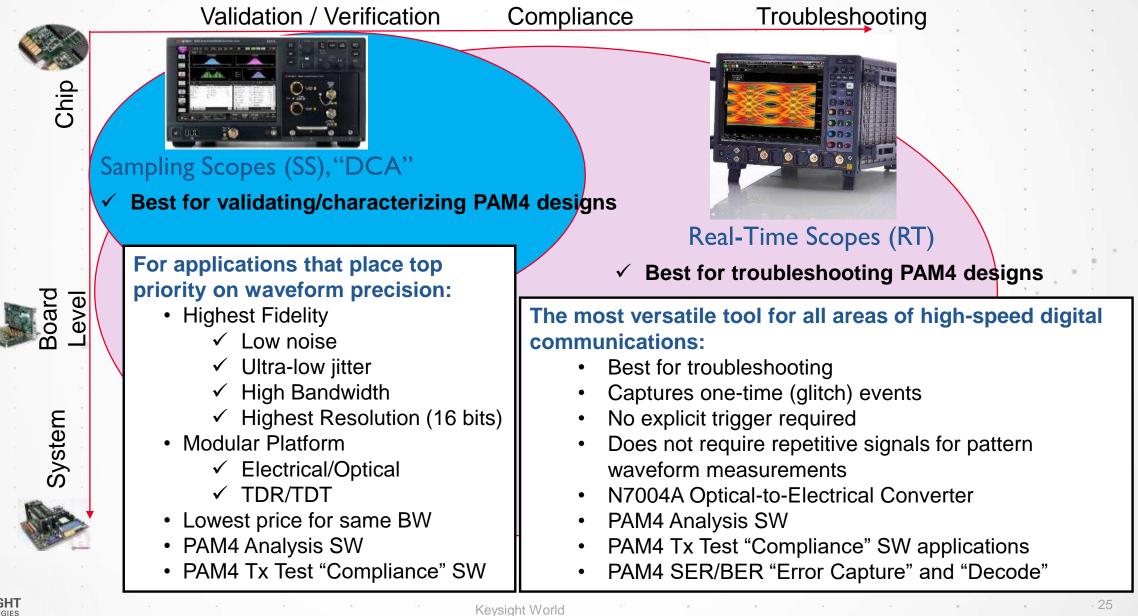

### Which Scope Should I Use to Characterize PAM4 Signals?

### **Key Measurements for Optical Direct Detection Tx**

**NRZ Transmitters**

- Optical Modulation Amplitude (OMA) (difference between the 1 level and 0 level)

- Extinction Ratio (ER) (ratio of 1 and 0 level)

- Transmitter Dispersion Penalty (TDP)

- Eye-mask

- Outer OMA (difference between the 3 level and 0 level)

- Outer ER (ratio of 3 and 0 level)

- Rise/fall times (per IEEE 802.3cd)

- Transmitter and dispersion eye closure for PAM4 (TDECQ)

- Replaces mask testing!

- Requires equalizers and "short patterns" (SSPRQ...no more PRBS31 for TX test).

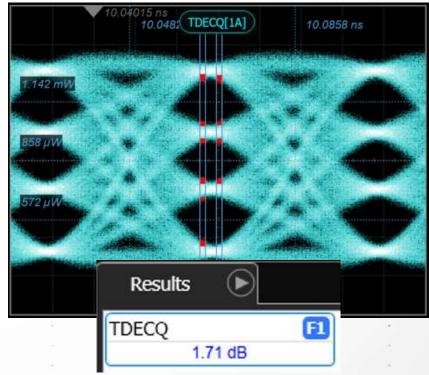

### **TDECQ**

#### TRANSMITTER DISPERSION AND EYE CLOSURE QUATERNARY

- Tells you the performance of your transmitter relative to an ideal transmitter

- For NRZ TDP, we literally used a BERT to measure the BER performance of the transmitter compared to an actual golden transmitter

- > Determine how much extra power was required at the receiver to compensate for non-ideal performance

- For TDECQ we indirectly measure SER (symbol error rate) using a scope, no BERT required

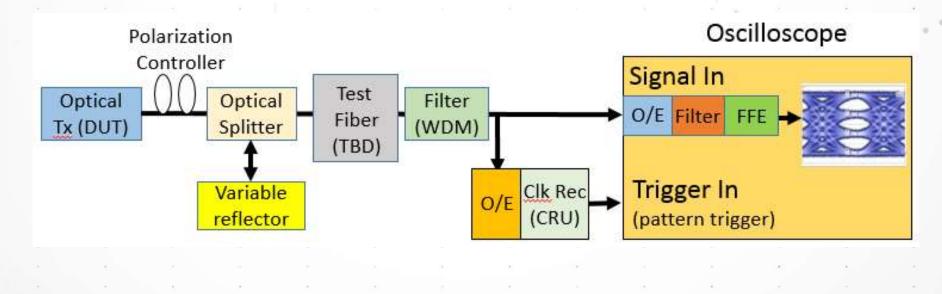

### **TDECQ Measurement Process**

#### FROM IEEE 802.3BS

- SSPRQ test pattern (2<sup>16</sup>-1 length)

- Includes test fiber dispersion (single-mode)

- Oscilloscope noise measured and mathematically 'backed out'

- Apply TDECQ equalizer

Virtual 5 tap, T spaced FFE reference equalizer (EQ taps optimized to minimize TDECQ penalty)

- Histograms constructed to assess eye closure relative to OMA and compute an effective power penalty in dB. This is the TDECQ result. (note: a smaller number is better)

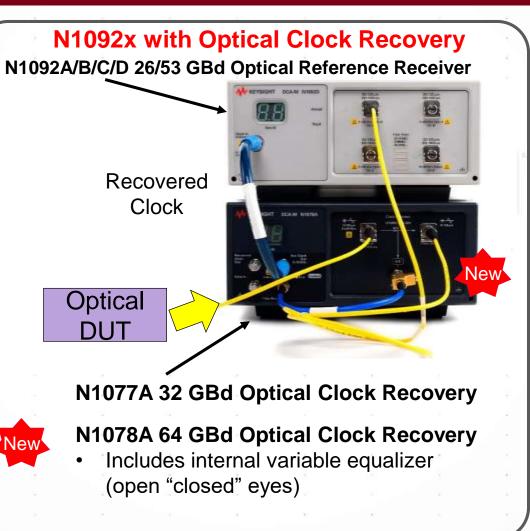

### **Keysight Scope Solutions for 26/53 Gbaud Optical Test**

#### FULLY COMPLIANT FOR ALL OPTICAL PAM4 APPLICATIONS

- 26/53 GBd Optical Ref RxMultimode and Single-Mode

- 1, 2, or 4 channels

- Low-noise receiver

- PAM4 analysis with TDECQ

FlexDCA User Interface: > Integrated PAM4 measurements results in FAST, EASY and COMPLIANT measurements

# Direct Detect Input (Receiver) Test

### **Input Testing Topics**

- Measurement challenges for 56 Gbaud (112 Gb/s) Rx characterization

- o Links do not run error free (by design) Avoid use of loopback to BERT ED

- New reference receiver

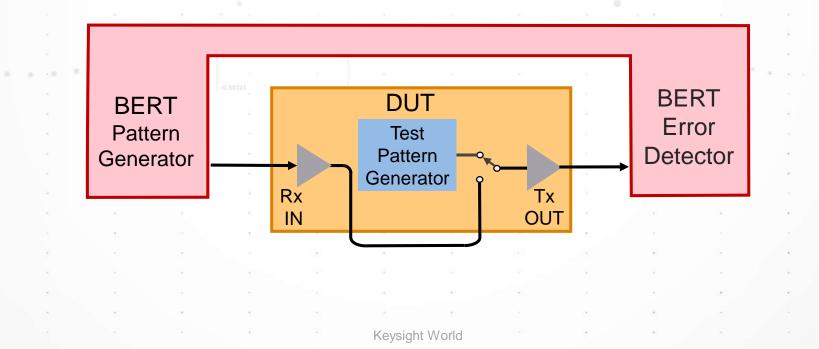

### Input Testing Links Which Don't Run Error Free (by design)

• The Bit Error Ratio Tester (BERT) will continue to be the principle tool for input testing

#### Traditional BERT input test setup

Clean loopback link required to prevent adding errors at BERT ED input

• Will the loopback path be error free in links designed to use FEC for error free operation?

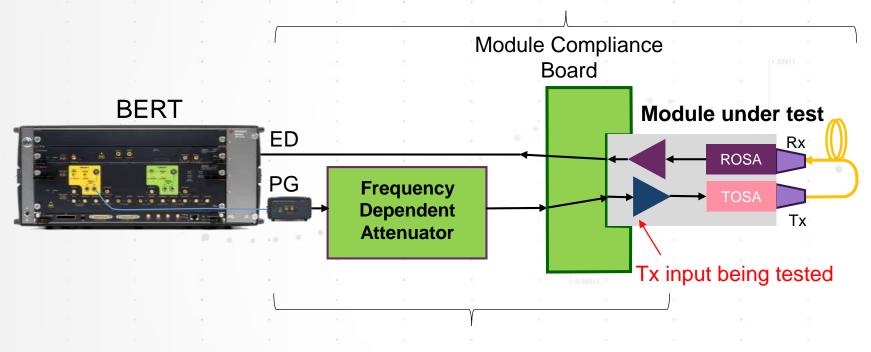

### IEEE 802.3 (100G) CAUI-4 C2M Tx Input Test

#### SAME TEST USED IN LEGACY MODULES (NRZ)

Required BER for entire link (C2M + Optical): 1E-12 (Error free)

- BERT PG + ISI channel provides stress signal to Tx input

- 2. Stressed signal drives optical Tx output through TOSA elements

- 3. Fibre patch cable provides loopback to optical Rx input of same or second ("golden") module to serve as O/E

- Looped back signal routed to BERT ED

Required BER for CAUI-4 C2M link: 1E-15, tested to 1E-12 (Error free)

Example: 100GBASE-LR4, Tx input (electrical) test, each lane tested independently

### **400G Requires a Different Test Method**

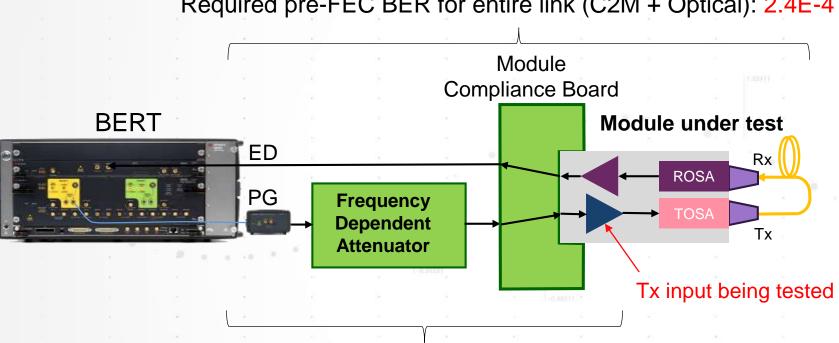

#### PAM4 LINKS DO NOT RUN ERROR FREE -> REQUIRES FEC

Required pre-FEC BER for entire link (C2M + Optical): 2.4E-4

Required pre-FEC BER for 200G AUI-4/ 400G AUI-8 C2M link: 1E-5

Example: 400GBASE-ER8 Tx input (electrical) test, each lane tested independently

- PAM4 links do not run error free Require Forward Error Correction (FEC) to achieve error free data

- All elements within the link contribute to errors, including the transmitter Distortion, skew, linearity, & noise

- Optical link has worse BER than C2M electrical link under test – should not be used as loopback path

- Errors at the BERT ED input will be added to actual errors detected from the Tx input under test – over stating the BER

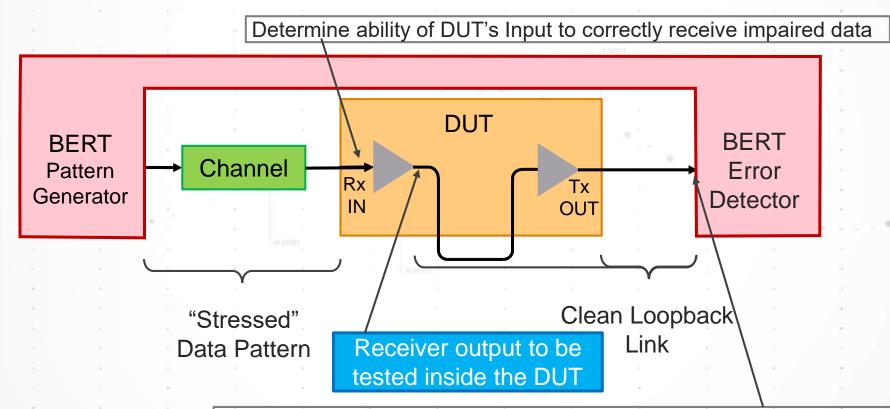

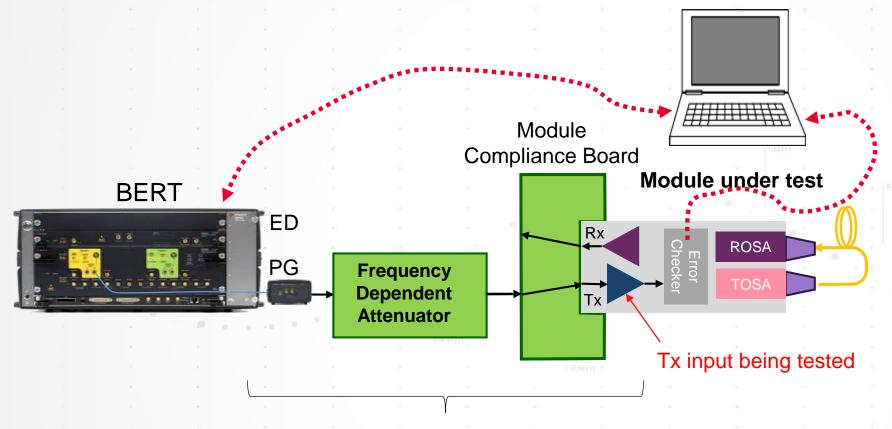

### **Preferred Input Test Method When Loopback Path is PAM4**

Required BER for 200G AUI-4/ 400G AUI-8 C2M link: 1E-5

Example: 400GBASE-ER8, each lane tested independently

- When error free loopback link cannot be assured (as in PAM-4 links), an internal error checker directly driven by input receiver under test should be used for accurate BER measurements

- BERT is still used to generate stressed test pattern, but not for error detection

- Error checker in DUT is read through alternate link, such as the management interface

- Data from DUT error checker can be read into Keysight M8070B System Software for M8000 BER test Solutions to enable direct JTOL and other measurements, identical capabilities as those made with BERT error detector

### **Chip Design Considerations for Receiver Testability**

- Use of internal error checkers eliminates degraded BER measurements from loopback path errors

PRBS31Q (same as OIF QPRBS31-CEI) is the standard test pattern for C2M compliance input testing

- If chip density does not allow internal error checker, consider adding PRBS-Q pattern generator

Pattern generator provides means to measure BER in loopback path only, isolated from receiver under test

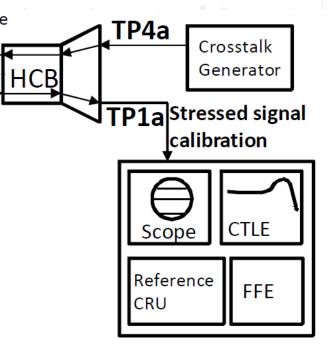

# **Challenges With Proposed Reference Receiver**

- The "Reference Receiver' normalizes the signal conditioning front end in test instruments used for Output (Tx) measurements and Input (Rx) stressed eye calibration

- Reference receiver is supposed to emulate a generic receiver implementation with minimal performance required to close the link budget

Reference: OIF CEI-112G-VSR Figure 23-10 Module Input Test Setup Draft ver. 07

Keysight World

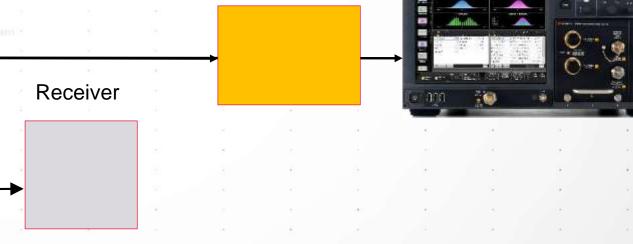

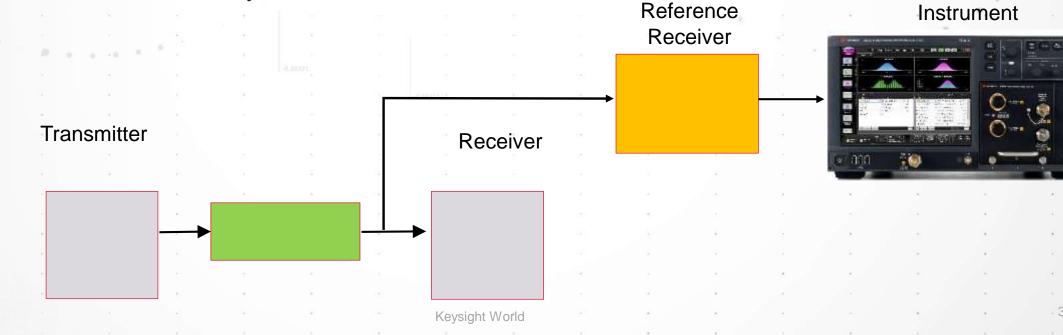

# Why is the Reference Receiver Needed?

- Problem measurement instrument may "see" artifacts in the link signal that will not impact the receiver

- e.g. higher frequency components beyond receiver bandwidth

- Solution add a "Reference Receiver" to constrain measurement to signals <u>as</u> seen by actual receiver

Kevsiaht World

- Removes out of band noise, DC from measurement

- Accuracy required for measurement repeatability

Transmitter

Reference

Receiver

Measurement

Instrument

# **The Reference Receiver**

Accurate measurement of what the DUT is seeing, results when reference receiver uses this approximation:

$$H_{DUT \text{ par.}}(x) = H_{\text{Ref.Rec.}}(x)$$

- Where  $H_{DUT par}(X)$  is the actual receiver response to the parameter being measured Measurement

- e.g. receiver's BW emulated by LPF in reference receiver

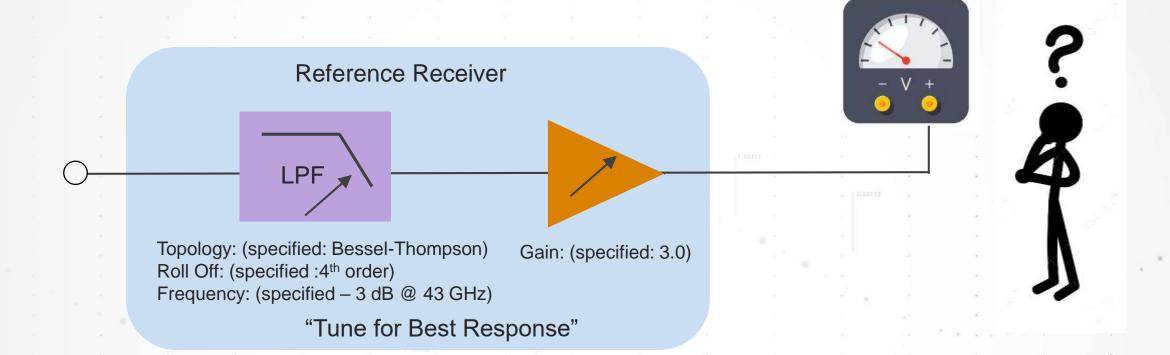

### **Optimizing Equalizers – Challenge Reference Receiver Concept**

- Traditionally, operational parameters of signal conditioning in front of test instrument are tightly specified for repeatable measurements

- Optimizing equalizer ("Tune for best response")

- OK for receiver, but challenges measurement repeatability

- Example self optimizing equalizer gives 50% UI EW in one case, with same Tx and channel, 58% in another.

Fine for a real receiver, but not a measurement instrument! (16% difference in EW measurements)

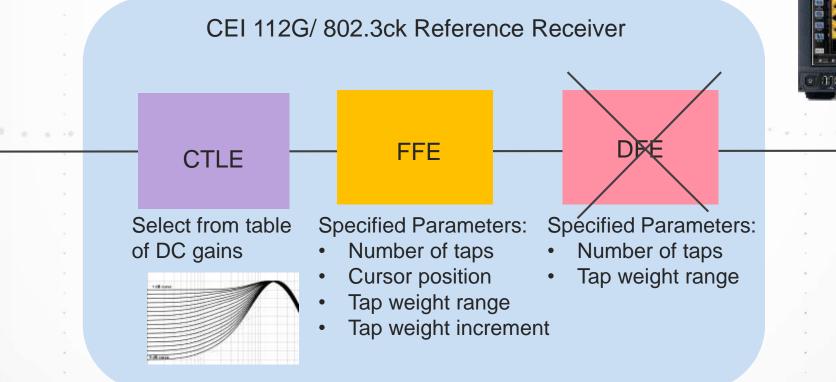

### **Current Equalizer Proposal**

- Cascaded equalizer CTLE + FFE and possibly DFE

- All stages are self optimizing

Measurement Instrument

# How to Make Self Optimizing Equalizer in RR Repeatable?

In theory optimizing equalizers could be used in reference receivers and give repeatable measurements when these conditions are met:

- Order of placement of equalizer elements (CTLE first, followed by <u>DFE or FFE</u>, followed by \_\_\_\_)

Linear systems should allow interchanging, but this ignores action of noise on individual equalizer elements

- Tap configuration

- Cursor placement

- Lange limits

- o Increment step size

- Optimization stop criteria

- Will actual implementations follow theory and be repeatable?

- o Concern with recent example TDECQ measurement (output Tx output in 400G 802.3cd standard project)

- TDECQ algorithm required several draft iterations to address non-repeatability between instrument vendors and poor correlation with BER results

- Large cause was found in self-optimizing TDECQ equalizer (FFE), and Ref RX model was not representative of actual RX

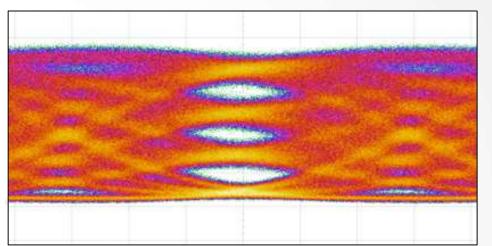

# **Coherent Optical Test**

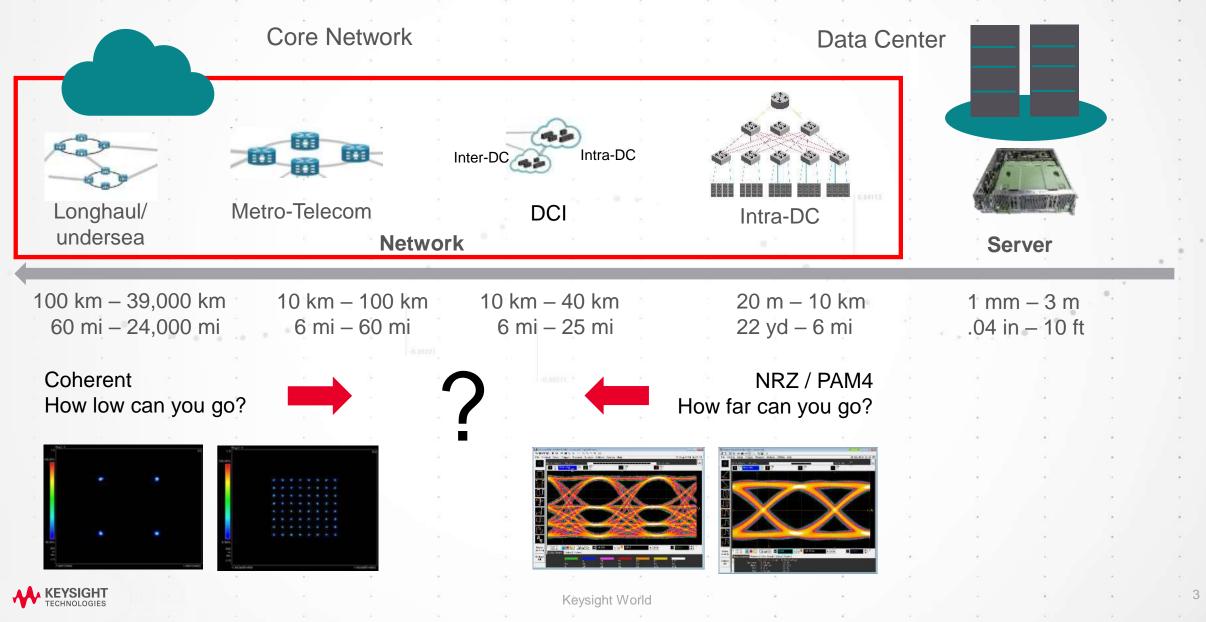

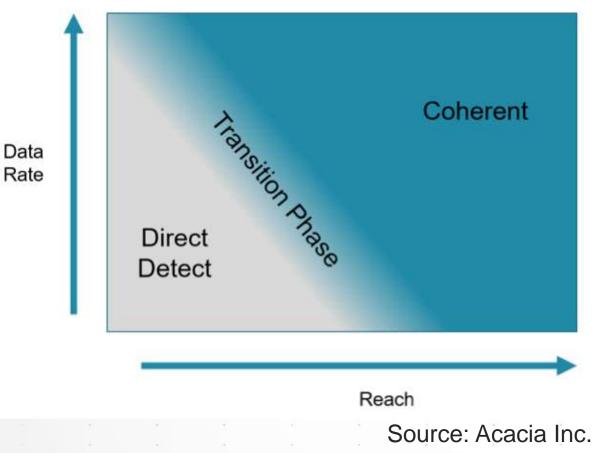

## **Coherent Moves into the Data Center**

#### COHERENT VS DIRECT DETECTION: A COST AND POWER GAME

#### **Direct Detection (PAM4)** Cost Power / Size Latency Needs CD compensation depending on link length Bandwidth (DWDM): 4 Tbit/s Coherent Cost Being addressed through reducing DSP requirements Power / Size and moving to 7 nm CMOS Latency DSP compensates CD adaptive to link length Bandwidth (DWDM): 20 / 30 Tbit/s with 16 / 64QAM

Keysight World

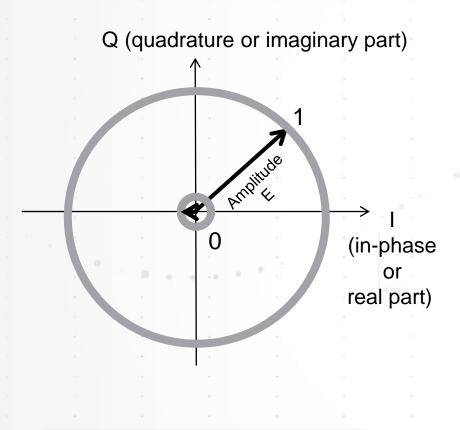

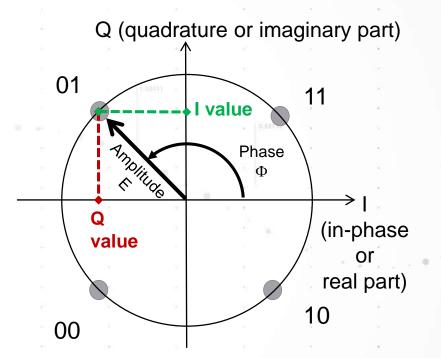

# **ON-OFF-Keying (OOK) vs. Digital Complex Modulation**

#### **GRAPHICAL REPRESENTATION**

1) Information is in amplitude

2) Phase can be random

1) Information is in amplitude

2) Information is in phase

# Analyzing Complex Modulated Signals with Conventional Direct Detection Methods?

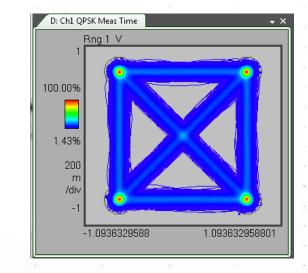

**QPSK** constellation map

Need amplitude AND phase sensitive measurement!

This is the region of transition between symbols

This is the region where the symbol/vector state should be stable and where communications quality is assessed

Keysight World

# Different Metrics Required for Direct Detection and Coherent Transmitters

#### OOK (NRZ / PAM4)

- Q-factor

- Eye mask (NRZ)

- TDECQ (PAM4)

- Timing jitter

- BER

- OSNR

**KEYSIGH**

#### Complex Modulation

- EVM

- IQ Imbalance, IQ Offset

- Quadrature Error

- Frequency Offset

- BER

- OSNR

Kevsight World

122

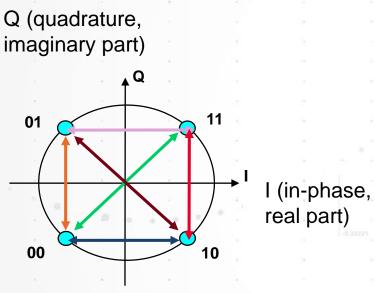

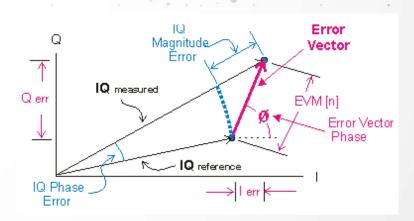

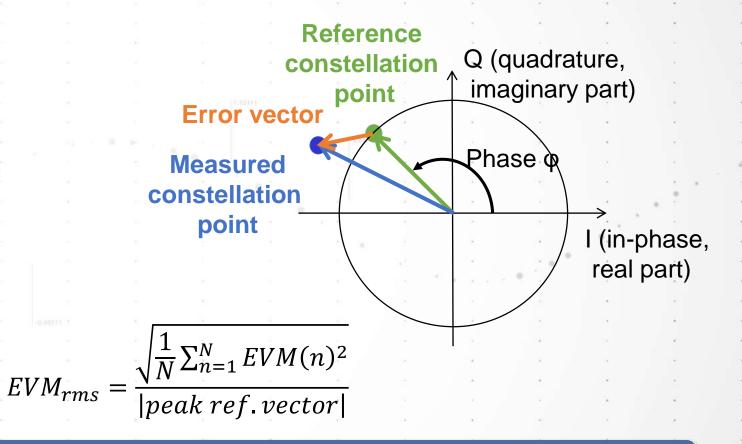

# **Error Vector Magnitude**

#### QUALITY MEASURE FOR COMPLEX MODULATED DATA SIGNALS

- Global quality metric for coherent Tx

- Needs reference receiver comprising

- Calibrated optical front-end

- Real-time ADC

- Defined signal processing blocks

The Error Vector connects the measured vector and the reference vector! An Error Vector = 0 means we have an ideal signal!

# **Method to Determine EVM**

#### ADDITIONAL IMPAIRMENT ANALYSIS FEATURES

#### M8290A

- ✓ Optimized for up to 400G signals

- ✓ Most compact

- ✓ Most affordable

- ✓ 4ch. 92 GSa/s

- ✓ 40 GHz

- ✓ 512 kSa memory

)IF ��IEEE

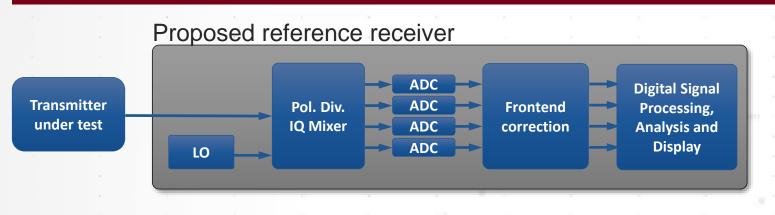

Proposed reference receiver for coherent transmitter testing:

- Dual-polarization coherent receiver

- Real-time signal acquisition (four synchronized ADC channels)

- Frontend correction

- Digital signal processing

Keysight supports these efforts in:

Reference receiver HW & SW

specified for the development

characteristics need to be

of an EVM specification

KEYSIGHT TECHNOLOGIES

Keysight World

# Outlook

#### LOOKING TOWARDS 800G

- First vertically integrated non-interoperable solutions announced by Infinera and Ciena

- Transmission rates from 100G to 800G

- Up to 100 Gbaud symbol rate

- Advanced signal processing methods like probabilistic constellation shaping and Nyquist sub-carriers

- Second generation of 800G solutions expected for 2021

- Lower power consumption

- Lower footprint

- o Interoperable

### N4391B OMA

- ✓ 4ch. 256 GS/s

- $\checkmark$  40 110 GHz BW options

- ✓ 200MSa 2 GSa memory

- ✓ Lowest noise floor

- ✓ Lowest skew

- ✓ 4ch. 120 GSa/s

- $\checkmark$  > 45 GHz 3-dB bandwidth

- ✓ Signal generation up to 50 GHz

- ✓ 512 kSa memory

DP-16 QAM constellation at **100 Gbaud** Optical measurement

# Layer 2-3 Test

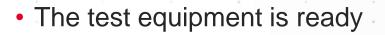

# 400G (PAM4) Changes What Needs to be Tested...

# **FEC Analysis is Critical**

#### 400GE STD, FEC, WHAT TO LOOK FOR

- Forward Error Correction (FEC)

- Corrects errors on the Receive side (Goal: no packet errors)

- FEC corrects up to 15 symbol errors per code word

- An uncorrectable code word results in equivalent of ~15 64B packets

Pre FEC BER 10^-4 Frame Loss Ratio No uncorrectable code words

### **HEALTHY?**

Look beyond "lack of CRC errors", pre FEC BER & FLR

Review how close to the limit of FEC

Monitor error distribution per physical lane

Monitor symbol error density

| FEC Total Bit Errors        | 1,685,086,529 |   |

|-----------------------------|---------------|---|

| FEC Max Corrected Symbols   | 15            |   |

| FEC Corrected Codewords     | 787,415,758   |   |

| FEC Total Codewords         | 8,747,730,910 |   |

| FEC Frame Loss Ratio        | 0.00e+000     |   |

| pre FEC Bit Error Rate      | 3.54e-005     | ) |

| FEC Codeword with 0 error   | 7,960,315,152 | - |

| FEC Codeword with 1 error   | 551,108,911   |   |

| FEC Codeword with 2 errors  | 200,069,411   |   |

| FEC Codeword with 3 errors  | 26,209,344    |   |

| FEC Codeword with 4 errors  | 8,176,726     |   |

| FEC Codeword with 5 errors  | 1,363,216     |   |

| FEC Codeword with 6 errors  | 382,557       |   |

| FEC Codeword with 7 errors  | 77,640        |   |

| FEC Codeword with 8 errors  | 21,150        |   |

| FEC Codeword with 9 errors  | 4,968         |   |

| FEC Codeword with 10 errors | 1,349         |   |

| FEC Codeword with 11 errors | 356           |   |

| FEC Codeword with 12 errors | 93            |   |

| FEC Codeword with 13 errors | 26            |   |

| FEC Codeword with 14 errors | 8             |   |

| FEC Codeword with 15 errors | 3             | - |

| EC Uncorrectable Codewords  | 0             |   |

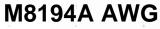

# **Introducing ARESONE-400GE**

# **Summary - Keysight Provides Industry Leading Tools**

#### FAST AND ACCURATE CHARACTERIZATION OF PAM4 DESIGNS

# **Questions?**

# Please stop by the demo booth

Keysight World

# **Data Center / Telecom Track Demos**

#### SEE AND HEAR THE LATEST AND GREATEST FROM INDUSTRY EXPERTS

#### **PCIe 5.0 Tx**

Signal Quality at PCIe 5.0 Speed Highest Signal Integrity at 32 GT/s Measure Highest Design Margins Simple Measurement Execution

#### **Signal Integrity**

Signal Distortion at 400G Speeds Precision 400G Measurements Extreme Bandwidth Over Copper End-to-end Characterization

#### <u>PCle 5.0 Rx</u>

Validating 32 GT/s Receivers Automated Rx Calibration Protocol Aware at 32 GT/s Interactive Link Training

Memory Design

Tedious Design/Test Cycles

Unified Design and Test

DDR Memory Designer

Test Plan Automation

#### DDR5 Tx

Double the Speed of DDR4 Complete Integrated Workflow Probe for Easy Signal Access Automated Test & Reporting

#### <u>400G Tx / Rx</u>

Moving from 400G to 800G and beyond Accurate 400G/800G measurements Full Tx Compliance testing of 400G designs Full PAM4 Signal Analysis

### DDR5 Rx Verify DDR Receivers at 6 Gb/s+ Full Speed & Accuracy Only Rx Compliance Test Solution

400G Network Validation Ensure 400GE Performance Verify QSFP-DD/OSFP Test 200/100/50GE Interoperability

# Acronyms

c2c = Chip-to-Chipc2m = Chip-to-ModuleBER = Bit Error Ratio BUJ = Bounded Uncorrelated Jitter (used to emulate crosstalk) DUT = Device Under Test EW = Eye WidthEH = Eye Height FEC = Forward Error Correction FFE = Feed-Forward Equalizer NRZ = Non-Return to Zero (Refers to 2 level signaling or PAM-2) PAM-n = Pulse Amplitude Modulation, where n = number of levels RJ = Random Jitter RS = Reed Solomon SER = Symbol Error Ratio SIRC – System Impulse Response Correction SJ = Sinusoidal Jitter SMF/MM F– Single-mode fiber, Multimode fiber TDP = Transmitter and Dispersion Penalty TDEC = Transmitter and Dispersion Eye Closure TDECQ = Transmitter and dispersion eye closure quaternary (for PAM4)