# Advanced Techniques for Validating the Latest Generation of PCIe Transmitters and Receivers

Francis Liu

2018.12.18&20

Senior Project Manager / Keysight Tech. AEO

### Agenda

- PCI Express 4.0 Timeline and 5.0 Roadmap

- PCI Express 4.0 TX / LTSSM Link EQ / RX Testing

- PCI Express 5.0 Preview

# Agenda

- PCI Express 4.0 Timeline and 5.0 Roadmap

- > PCI Express 4.0 TX / LTSSM Link EQ / RX Testing

- > PCI Express 5.0 Preview

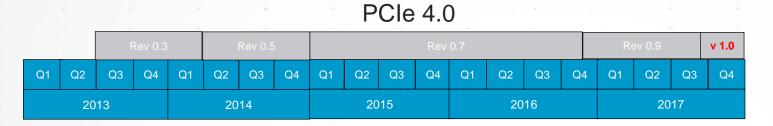

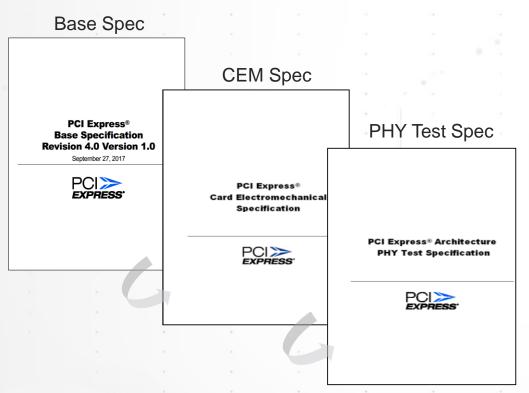

# PCI Express 4.0 Timeline & 5.0 Roadmap

### **PCI Express 4.0 New Features**

### Based on PCIe v1.0 BASE specification

- New data rate:16GT/s

- · Requires an output stages capable of providing pre-shoot and de-emphasis with fast enough rise-times.

- Link Equalization protocol similar to PCle 3.0

- TxEQ P0-P10

- RxEQ CTLE (2 pole 1 zero) + 2tap DFE

- Max Channel Loss -28dB @ 8GHz & 1 connector

- Re-timers used for longer channels or for channels with >1 connector

- RX clocking architectures: CC and IR

- CC -> Common RefClock -> synchronous RX and TX w/ or w/o SSC

- IR -> Independent RefClock -> asynchronous RX and TX w/ or w/o SSC

- Initial LinkEQ speed selection: 2.5GT/s -> 8GT/s with link equalization

- if successful -> Then transitions to 16GT/s with another round of link equalization

- TX Jitter Analysis: Similar to PCle 3.0

- RX Lane Margining added.

# **CEM 4.0 and Compliance Testing**

- CEM 4.0 currently at v0.7

- V0.7 in CEM Review

- PCle 4.0 Compliance Requirements

- CEM Spec completion at v0.7 (v0.9 optimal)

- Completion of Test Specifications

- Config Test Spec

- Link Transaction Test Spec

- System Firmware (BIOS) Test Spec

- Electrical Test Spec

- Retimer Test Spec

- Availability of Gen4 Compliance Test Fixtures for Purchase

- New order collection in Nov.

- Estimated Schedule

- First Gen4 FYI testing commenced April 2017

- Official FYI Testing to begin 2018

- PCI-SIG Developers Conference 2018 is returning to Santa Clara, June 5-6, 2018

- Official Integrators list test to start mid 2018

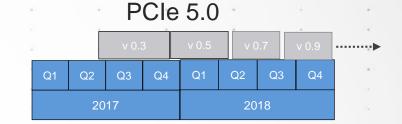

# PCI Express® Card Electromechanical Specification Revision 4.0, Version 0.7 DRAFT

March 22, 2018

### PCI Express Architecture PHY Test Specification

Revision 4.0, Version 0.7

November 8, 2018

### Agenda

- > PCI Express 4.0 Timeline and 5.0 Roadmap

- PCI Express 4.0 TX / LTSSM Link EQ / RX Testing

- > PCI Express 5.0 Preview

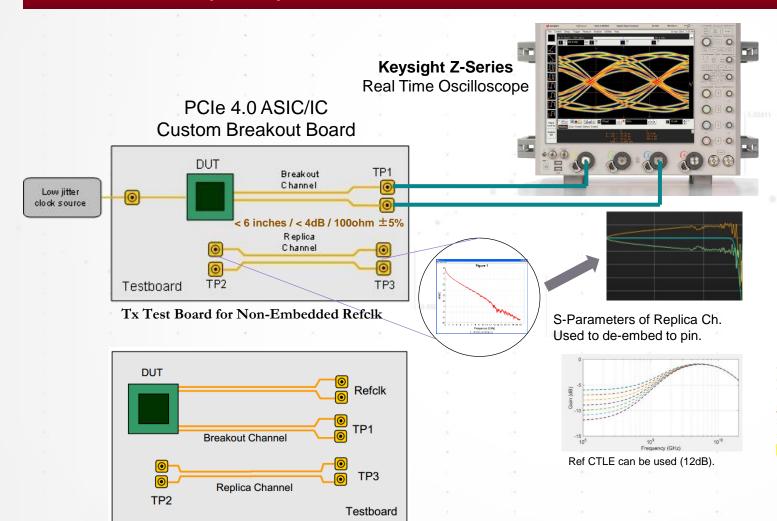

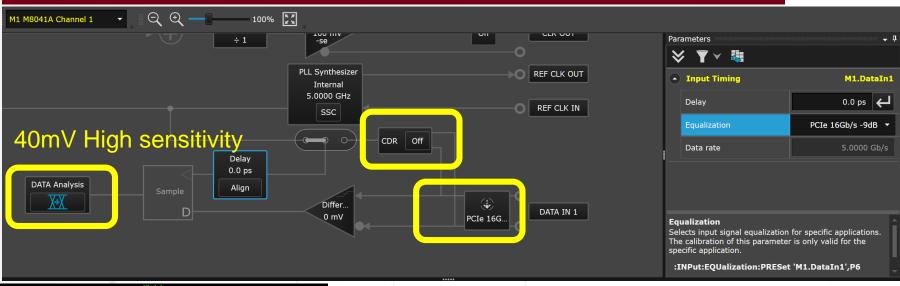

# PCIe 4.0 Base Spec TX Measurement Basic Test Setup Tx Test Scope Bandwidth Requirement

BASE SPEC (V1.0)

#### 8.3.5.2 Applying CTLE or De-embedding

Direct probing at a Transmitter's pins is not generally feasible, so data is instead measured at TP1 of the breakout channel. By means of the replica channel it is possible to determine the loss vs. frequency characteristics of the breakout channel and de-embed this channel, resulting in measurements that are effectively referenced to the DUT's pins. Note that since de-embedding amplifies HF noise there is a practical frequency cutoff limit to de-embedding. As de-embedding amplifies HF channel and measurement noise, an HF cutoff limit of 8GHz-12GHz and 20 GHz (3dB point) must be applied to de-embedding, depending on data rate as shown in Table 8-5.

Table 8-5: Recommended De-embedding Cutoff Frequency 20GHz

|           |                     | LUGIT          |

|-----------|---------------------|----------------|

| Data Rate | HF Cutoff limit for | De-embed limit |

| 8GT/s     | 8GHz-12 GHz         | De embed innit |

| 16GT/s    | 20GHz               |                |

#### 8.4.2.1 Procedure for Calibrating a Stressed EH/EW Eye

As the calibration procedure of the signal generator output contains steps where the generator is connected directly to measurement instrumentation, the transition time of the output waveform can be very fast. Therefore, it is important that the bandwidth of instrumentation used to calibrate the generator be matched appropriately to the edge rate of the generator output. This specification requires the use of a generator whose outputs have a rise time of 14ps-19ps (20% / 80%) which also requires a minimum oscilloscope bandwidth of 25GHz. This oscilloscope bandwidth is also the minimum required bandwidth for transmitter measurements.

25GHz Min Scope BW

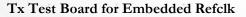

# PCIe 4.0 TX Test with Keysight N5393F Application

Compliance Test SW Features

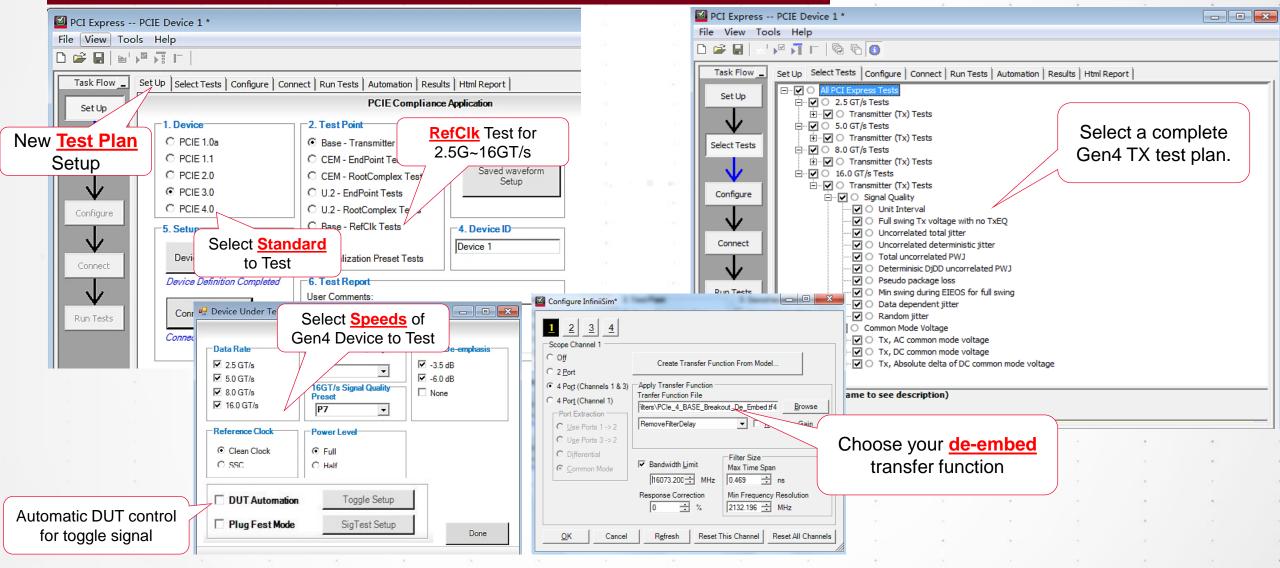

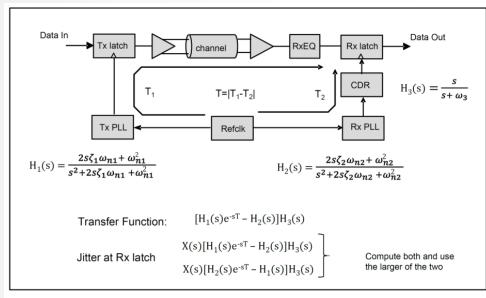

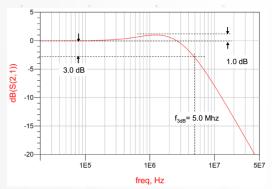

### **PCIe4.0 Reference Clock Measurement**

Show Spec in Report

Figure 8-57: Common Refclk Rx Architecture

PLL Jitter Transfer Function Example

Table 8-21: Common Refclk PLL and CDR Charactustics for 8.0 and 16.0 GT/s

| Г |                                                            |                                                       |                                                         |  |                                      |                                           |                                              |  |

|---|------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------|--|--------------------------------------|-------------------------------------------|----------------------------------------------|--|

|   | PLL #1                                                     | 0.01 dB peaking                                       | 2.0 dB peaking                                          |  | PLL #2                               | 0.01 dB peaking                           | 1.0 dB peaking                               |  |

|   | BW <sub>PLL</sub> (min) = 2.0<br>MHz                       | $ω_{n1}$ = 0.448 Mrad/s $ζ_1$ = 14                    | $\omega_{\rm n1}$ = 6.02 Mrad/s $\zeta_1$ = 0.73        |  | BW <sub>PLL</sub> (min) = 2.0<br>MHz | $ω_{n2}$ = 0.448 Mrad/s $ζ_2$ = 14        | $\omega_{n2}$ = 4.62 Mrad/s $\zeta_2$ = 1.15 |  |

|   | BW <sub>PLL</sub> (max) = 4.0<br>MHz                       | $\omega_{\rm n1}$ = 0.896 Mrad/s $\zeta_{\rm 1}$ = 14 | $\omega_{\rm n1}$ = 12.04 Mrad/s $\zeta_{\rm 1}$ = 0.73 |  | BW <sub>PLL</sub> (max) = 5.0<br>MHz | $\omega_{n2}$ = 1.12Mrad/s $\zeta_2$ = 14 | $ω_{n2}$ = 11.53 Mrad/s $ζ_2$ = 1.15         |  |

|   | BW <sub>CDR</sub> (min) = 10<br>MHz, 1 <sup>st</sup> order | 64 combinations 8.0, 16.0 GT/s                        |                                                         |  |                                      |                                           |                                              |  |

|       |      |       |      | REF Cloc | k 8G TX Pl | hase Jitter |      |     |     |

|-------|------|-------|------|----------|------------|-------------|------|-----|-----|

|       | 4    |       | PLL1 |          |            |             | • PL | L 2 |     |

| H     | (0.1 | ATX   | BTX  | СТХ      | DTX        | ATX         | BTX  | СТХ | DTX |

|       | ARX  | 100   | ₽    | *(       |            |             | 90   |     |     |

| PLL 1 | BRX  | 0.60  | 5    | =        | -          |             | (4)  | 3.0 |     |

| ъ.    | CRX  | 1.80  | 6    | 11       | 0.3 ps     | 7,9ps       | 0.99 |     | Ne  |

| 14    | DRX  | 1.82  | 12   | 1        |            |             |      |     |     |

| 18    | ARX  | 5.651 | E2   |          |            |             |      |     | 1.5 |

| PLL 2 | BRX  | (20)  | 5.   |          |            | 7           | 18   |     |     |

|       | CRX  | 580   | E :  |          |            |             |      |     |     |

|       | DRX  | te.   |      |          |            |             | 177  |     |     |

If user right clicks on a curve, pop up menu shows curves related to the calculation of that value.

Color code fields for PASS/Fail/Margin

Report Results in a Matrix

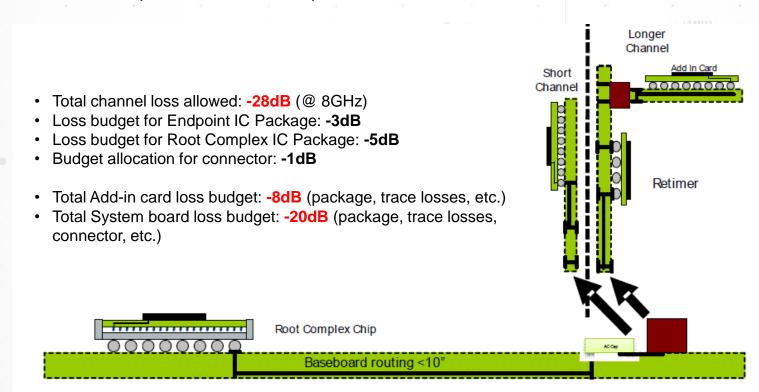

### **PCI Express Channels for PCIe 4.0**

- Card Electromechanical (CEM) form factor

- ✓ Channel length limited to ~12 inches and one connector.

- ✓ Retimer required if longer channel or more than 1 connector required.

- ✓ Maximum 2 Retimers are permitted between Upstream and Downstream.

### **PCIe 4.0 CEM TX Test Requirements**

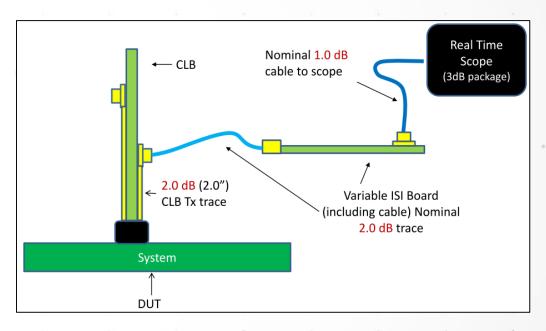

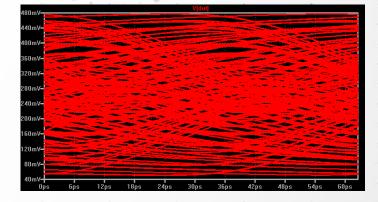

### PCle 4.0 (System) Tx Signal Quality Test at 16 GT/s

**Channel Setup**

Scope BW is set to 25GHz for CEM compliance CLB plugs into system -> Variable ISI Board -> Scope

8dB at 8GHz of additional loss (including package employed)

Power on System

Scope bandwidth = 25GHz

3dB package model embedded on scope

Toggle DUT to transmit 16GT/s Compliance Pattern

• 1ms pulse of 100MHz clock signal into Rx Lane0

Capture 2.0M UI waveform for every Tx EQ Preset

Waveforms post processed using SigTest

Ref clock captured with data waveform and used for clock recovery

Behavioral Rx

Eve width & Ev

Each lane mus

• EW > 0.3U

EH > 15m\

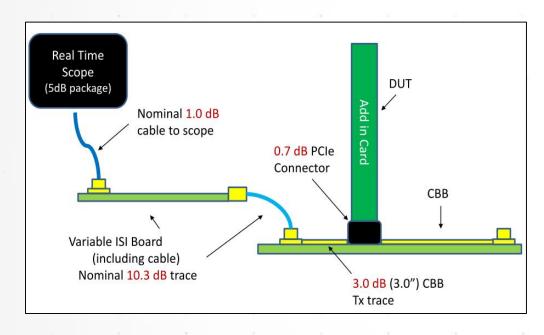

PCIe 4.0 (Add-in Card)

Tx Signal Quality Test at

**Channel Setup**

for CEM compliance Add-in Card plugs into CBB -> Variable

Scope BW is set to 25GHz

20dB at 8GHz of additional loss (including)

areage embedding)

Power on CBB

Scope bandwidth is 25GHz

5dB package model embedded on scope

Toggle DUT to transmit 16GT/s Compliance Pattern

· 1ms pulse of 100MHz clock signal into Rx Lane0

Capture 2.0M UI waveform for every Tx EQ Preset

Waveforms post processed using SigTest

· Time Domain CDR algorithm used to recover clock

· Behavioral Rx Equalization applied

Eye width & Eye height @ E-12

Each lane must pass SigTest analysis for at least one Tx EQ Preset

. EW > 0.3UI (with TBD adjustment due to lack of cross-talk, etc. in test fixtures)

EH > 15mV (with TBD adjustment due to lack of cross-talk, etc. in test fixtures)

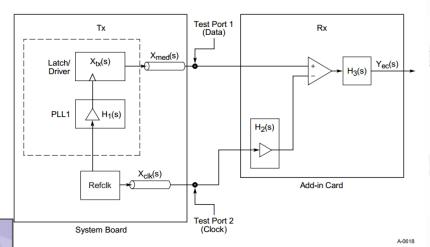

The system board Transmitter path measurements at 16.0 GT/s are made using a two-port measurement methodology. Figure 33 shows a functional block diagram for a system board and Add-in Card that shows the measurement points for the two-port method.

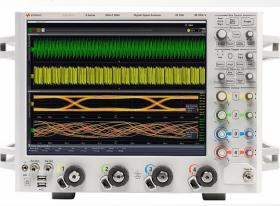

**Keysight Z-Series 25GHz RT Oscilloscope**

Dual Port Test (4 Channels) with 25GHz BW D+ D- CLK+ CLK- Capture Simultaneously

Figure 35: 16 GT/s Two Port Measurement Functional Block Diagram

#### 2.8.3. System Board Transmitter Electrical Compliance Test for 16.0 GT/s s

- 1. Connect the Tx lane under test to the input of the CBB Variable ISI board (choosing the lane which gives a total loss of 15dB @ 8GHz). Connect the output of the CBB Variable ISI board to a high speed oscilloscope or equivalent data capture instrument via low loss SMA cables.

- 2. If the correct Transmitter Equalization setting is known, push the compliance toggle button on the CLB (inject a 1 ms pulse of a 100 MHz clock signal into receive lane zero of the motherboard under test) until the correct Tx EQ is selected, otherwise push the compliance toggle button until the initial 16 GT/s Tx EQ preset is selected.

- 3. Measure transmitted clock and data waveforms simultaneously with a high speed oscilloscope or equivalent data capture instrument.

- 4. Confirm that the waveform is the correct compliance pattern.

- 5. Capture 1.6 million unit intervals of data  $(2.0 \times 10^6 \times 62.5 \text{ps} = 100.0 \mu\text{s})$ .

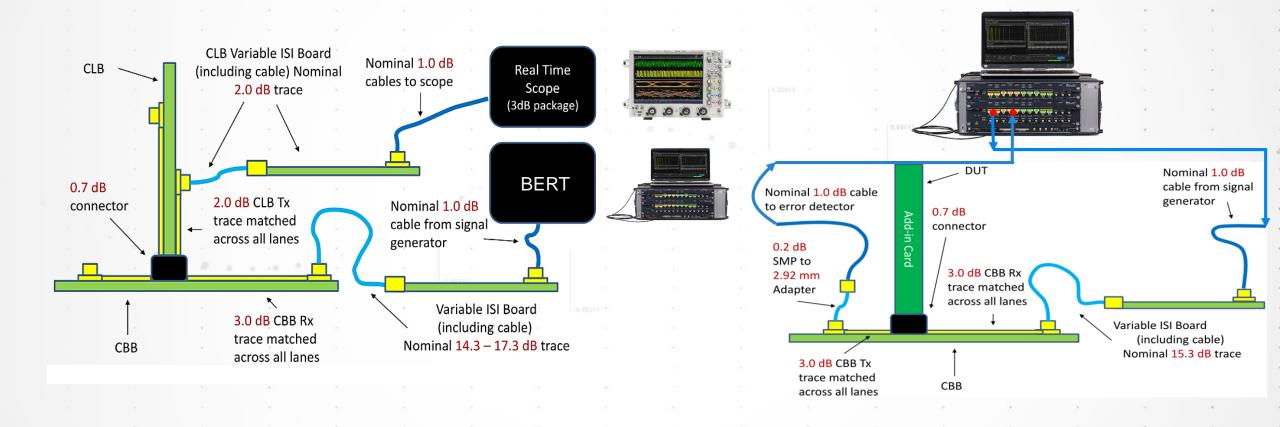

### PCIe 4.0 CEM TX Test Setups

### AIC and Motherboard Test Proposals

#### **Add-in Card TX Test**

#### **Motherboard TX Test**

Note: This TX test proposal utilizes an external variable ISI board to ensure consistent insertion loss of the test setup.

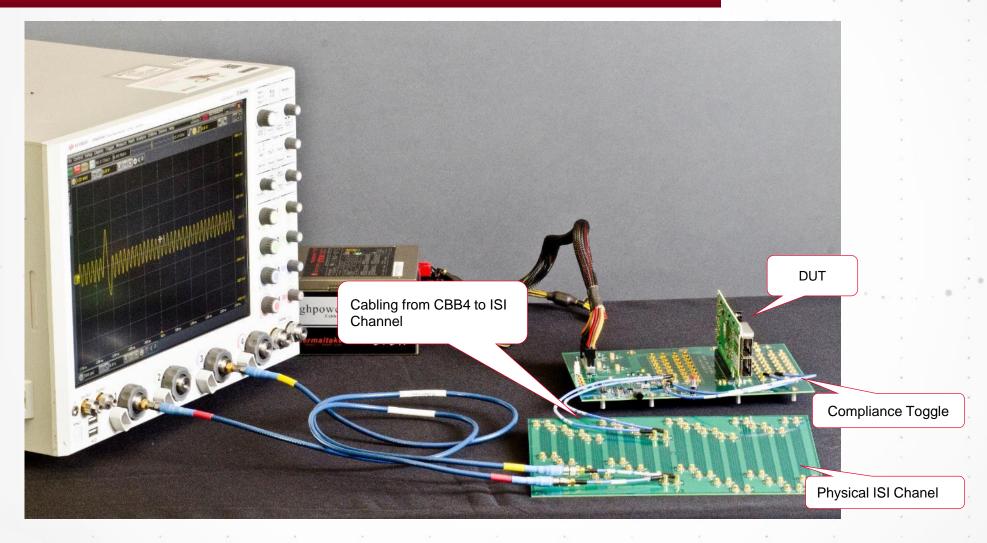

# PCIe 4.0 CEM TX Test Setup Example

### CEM AIC Setup With Scope

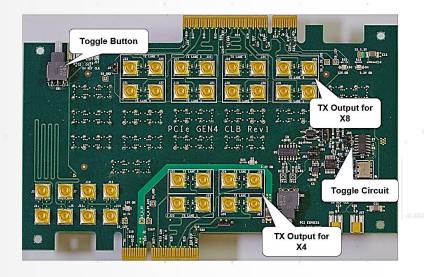

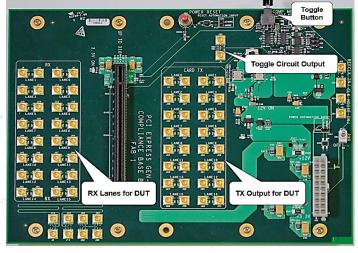

# **PCIe 4.0 CEM TX Test Fixtures**

### **CEM Test Fixture Set**

### CLB4 x4-x8 Fixture

### **CBB4 Fixture**

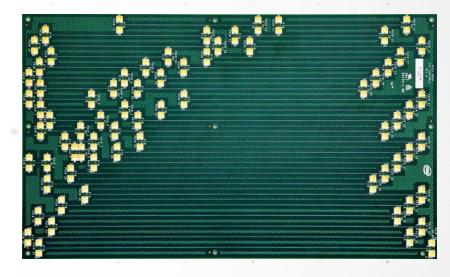

### **ISI Fixture**

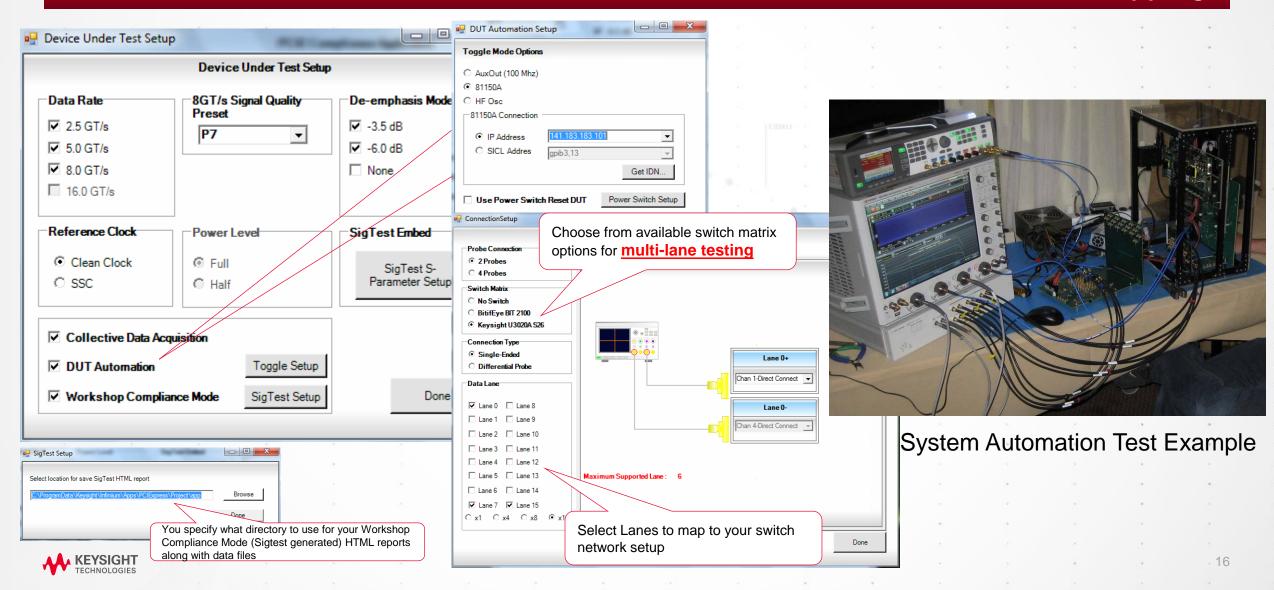

# **Speeding up Testing With N5393F Test Application**

Automated DUT Control, SIGTEST Mode and Enhanced Switch Matrix Lane Mapping

# Gen4 Tx testing test spec. and latest SigTEST version

# 2.7.5 System Board Transmitter Electrical Compliance Test for 16.0 GT/s

- 1. Connect the Tx lane under test on the CLB to the differential pair of the Variable ISI board which provides a physical channel insertion loss of 5dB at 8 GHz (See Appendix C). Connect the output of the Variable ISI board to a high-speed oscilloscope or equivalent data capture instrument via low loss SMA cables.

- 2. Connect the Reference Clock (REF CLK) on the CLB to a high-speed oscilloscope or equivalent data capture instrument via low loss SMA cables.

- 3. If the correct Transmitter Equalization setting is known, push the compliance toggle button on the CLB (inject a 1 ms pulse of a 100 MHz clock signal into receive lane zero of the motherboard under test) until the correct Tx EQ is selected, otherwise push the compliance toggle button until the initial 16 GT/s Tx EQ preset is selected.

- 4. Measure transmitted clock and data waveforms simultaneously with a high-speed oscilloscope or equivalent data capture instrument with the maximum bandwidth set to 25GHz

- 5. Confirm that the waveform is the correct compliance pattern.

- **6.** Capture 2.0 million unit-intervals of data and clock (2.0  $\times$  10<sup>6</sup>  $\times$  62.5ps = 125.0μs) simultaneously.

Note: The Non-Root Complex package model will be embedded into the captured data waveform on the scope or by Sigtest. The s-parameters to be embedded are included with this specification.

- 7. Measure Extrapolated Eye Height and Minimum Eye Width using SigTest analysis program with the appropriate choice of template file (PCIE\_4\_0\_SYS\

PCIE\_4\_16GB\_CEM\_DUAL\_PORT.dat).

- **8.** The SigTest analysis program will also indicate if the acquired data pattern matches the expected compliance pattern. (this check is informative)

- 9. If the SigTest analysis program indicates the system board Minimum Eye Width is greater than or equal to 21.75ps and Extrapolated Eye Height is greater than or equal to 19mV, the, electrical compliance test passes and is complete. If SigTest indicates the system board fails, the next Tx EQ setting should be selected (by pushing the compliance toggle button) and steps 3 through 8 of this test procedure should be repeated until the system board passes or all Tx EQ settings have been tested.

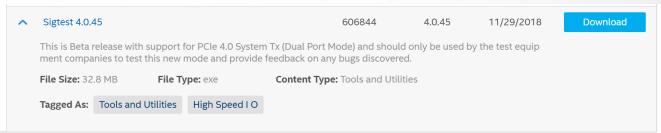

https://www.intel.com/content/www/us/en/design/technology/high-speed-io/tools.html?grouping=rdc%20Content%20Types&sort=title:asc

PCI Express Architecture PHY Test Specification Revision 4.0, Version 0.7

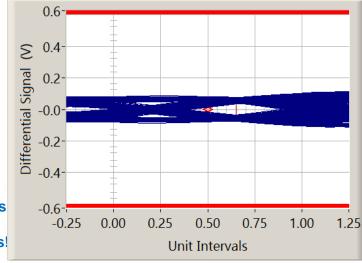

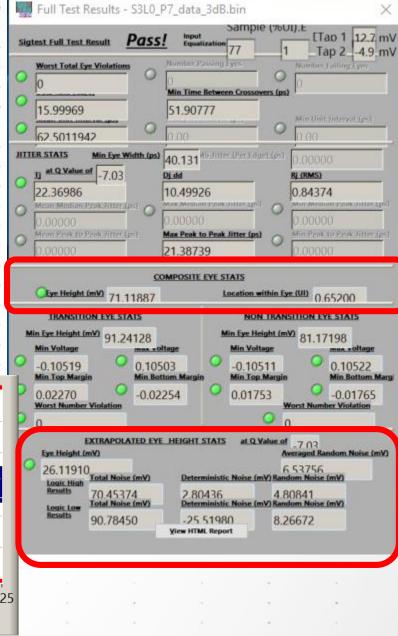

# SigTest 4.0.45 test report

#### SYSTEM BOARD EXAMPLE

#### Sigtest:

- Overall Sigtest Result: Pass!

- Mean Unit Interval (ps): 62.501194

- Min Time Between Crossovers (ps): 51.907773

- Data Rate (Gb/s): 15.999694

- Max Peak to Peak Jitter: 21.38739 ps

- Total Jitter at BER of 10E-12: 22.369856 ps

Total Jitter at BER of 10E-12 Passes Sigtest Limits!

- Minimum eye width: 40.130144 ps

- Deterministic Jitter Delta-Delta: 10.499261 ps

Deterministic Jitter Delta-Delta Passes Sigtest Limits!

- Random Jitter (RMS): 0.843742 ps

Random Jitter (RMS) Passes Sigtest Limits!

- Minimum Transition Eye Voltage: -0.105189 volts

Minimum Transition Eye Voltage Passes Sigtest Limits!

- Maximum Transition Eye Voltage: 0.105026 volts

Maximum Transition Eye Voltage Passes Sigtest Limits!

- Composite Eye Height: 0.071119

- Composite Eye Location: 0.652

Composite Eye Height Passes Sigtest Limits!

- Minimum Transition Eye Voltage Margin Above Eye: 0.022703 volts

Minimum Transition Eye Voltage Margin Above Eye Passes Sigtest Limits

- Minimum Transition Eye Voltage Margin Below Eye: -0.022538 volts

Minimum Transition Eye Voltage Margin Below Eye Passes Sigtest Limits!

- Minimum Transition Eye Height: 0.091241 volts

#### **TEMPLATE FILE SETTINGS**

- •Template File: PCIE\_4\_0\_SYS \ PCIE\_4\_16GB\_CEM\_DUAL\_PORT

- •Nominal Data Rate (bits/sec): 1599999999999998

- ·Target Unit Interval (s): 6.25e-011

- •Minimum Time Allowed Between Crossovers (s): 4.0e-011

- Minimum Data For Testing (UI): 200

- Ambiguous UI Resolution Method: EYE\_AMBIGUOUS\_NONE (0)

- •Tj@E-12 Peak to Peak Jitter Limit (s): 4.075e-011

- •CTLE equalization index = 1

- •DFE equalization: Tap 1 = 12.695312, Tap 2 = -4.882812

- Sigtest Version: 4.0.45

# SigTest result vs. Keysight SDA tool

#### SIGTEST STILL IN BETA VERSION!!!!

# PCIe 4.0 LinkEQ and Receiver Testing at 16Gbps

Jitter and De-emphasis

### Link Equalization

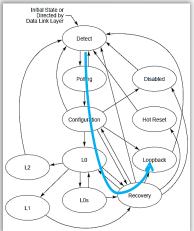

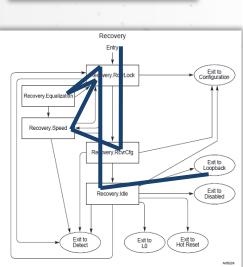

Phase 0: EQ TS2 Ordered Sets send from Downstream Port to Upstream Port.

Phase 1: Both sides exchange TS1 Ordered Sets to establish an operational Link. EIEOS sent every 32 TS1 Ordered Sets

Phase 2: Upstream Port requests boundsteam Port to set its Transmitter's coefficients/presets to have its incoming Link meet the electrical requirements. The Downstream Port may send an EIEOS in up to 65538 TS1 Ordered Sets, based on the Upstream Port's request. The Upstream Port sends an EIEOS every 32 TS1 Ordered Sets.

Phase 3: Downstream Port requests Upstream Port to set its Transmitter's coefficients/presets to have its incoming Link meet the electrical requirements. The Upstream Port may send an EIEOS in up to 6558 TSI Ordered Sets, based on the Downstream Port's request. The Downstream Port sends an EIEOS every 32 TSI Ordered Sets.

#### Equalization Complete

Post Equalization: LTSSM goes through Recovery.RovrLook, Recovery.RovrCfg, and Recovery.Idle to L0. EIEOS sent after every 32 TS1/TS2 Ordered Sets.

A-0809

# Differences between PCIe Gen3 and PCIe Gen4 Relevant changes with PCIe 4.0 rev 0.5 and 0.7

|                               |                                                           | PCIe 3.0/3.1                                                                                 | PCIe 4.0 rev 0.5                                                                            | Outlook PCle 4.0 rev 0.7                                   |  |  |  |

|-------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

|                               | added transfer rate                                       | 8 GT/s 16 GT/s                                                                               |                                                                                             |                                                            |  |  |  |

|                               | coding                                                    |                                                                                              | 128B/130B                                                                                   |                                                            |  |  |  |

|                               | block alignment & scrambler reset                         |                                                                                              | EIEOS for block alignment                                                                   |                                                            |  |  |  |

|                               | EIEOS                                                     | 10<br>00FF 00FF 00FF 00FF 00FF<br>00FF 00FF 00                                               | 10<br>00FF 00FF 00FF 00FF 00FF<br>00FF 00FF 00                                              | 10<br>0000 FFFF 0000 FFFF 0000<br>FFFF 0000 FFFF → 500 MHz |  |  |  |

| Link EQ gets more importa     | scrambling                                                | control: no (partially), data: always PRBS 2 <sup>23</sup> -1; scrambler reset through EIEOS |                                                                                             |                                                            |  |  |  |

|                               | Adaptable TX link equalization                            | yes                                                                                          | yes, two step process: first 8G link eq followed by 16G link eq if 8G link eq is successful |                                                            |  |  |  |

| Different cal precedure       | RX tests                                                  | stressed jitter test and stressed voltage test                                               | one RX stress test                                                                          |                                                            |  |  |  |

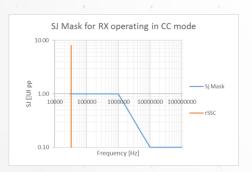

| Different cal procedure       | 155C for common reference clock                           | no                                                                                           | no                                                                                          | yes                                                        |  |  |  |

|                               | eye opening after reference RX for stress signal cal      | 0.3 UI, 25 mV, BER of 10 <sup>-12</sup>                                                      | 0.3 UI, 15 mV (RX eye spec. is actually 14 mV), BER of 10 <sup>-1</sup>                     |                                                            |  |  |  |

|                               | stress signal adjustment using                            | RJ, DM-SI and V <sub>diff</sub>                                                              | coarse: ISI<br>fine: DM-SI + SJ or DM-SI + V <sub>d</sub>                                   | liff                                                       |  |  |  |

| Special cal channel fixture i | required ;TLE changes:  pole 1 frequency → affects RX cal | 2 GHz                                                                                        | 4 GHz                                                                                       | 2 GHz                                                      |  |  |  |

|                               | Channel for RX test                                       | No connector required                                                                        | PCIe 4.0 CEM connector required as part of RX test channel                                  |                                                            |  |  |  |

# There is no Rx Jitter tolerance in Gen 4 test spec.

### ONLY TX/RX LINK EQ TEST ITEMS

| 2.4   | l Ad    | ld-in Card Transmitter Initial TX EQ Test                                     | 15 |

|-------|---------|-------------------------------------------------------------------------------|----|

| 2     | 2.4.1   | Starting Configuration                                                        | 15 |

| 2     | 2.4.2   | Add-in Card Transmitter Initial TX EQ test for 8.0 GT/s                       | 15 |

| 2     | 2.4.3   | Add-in Card Transmitter Initial TX EQ test for 16.0 GT/s                      | 16 |

| 2.5   | 5 Ad    | d-in Card Transmitter Link Equalization Response Test                         | 17 |

| 2     | 2.5.1   | Starting Configuration                                                        | 17 |

| 2     | 2.5.2   | Add-in Card Transmitter Link Equalization Response Test for 8.0 GT/s          | 17 |

| 2     | 2.5.3   | Add-in Card Transmitter Link Equalization Response Test for 16.0 GT/s         | 18 |

| 2.6   | 6 Ad    | ld-in Card Lane Margining at 16 GT/s                                          | 19 |

| 2.7   | ' Sy    | stem Board Transmitter Signal Quality                                         | 20 |

| 2     | 2.7.1   | Starting Configuration                                                        | 20 |

| 2     | 2.7.2   | Overview of Test Steps                                                        | 20 |

| 2     | 2.7.3   | System Board Transmitter Electrical Compliance Test for 2.5 GT/s and 5.0 GT/s | 21 |

| 2     | 2.7.4   | System Board Transmitter Electrical Compliance Test for 8.0 GT/s              | 21 |

| 2     | 2.7.5   | System Board Transmitter Electrical Compliance Test for 16.0 GT/s             | 22 |

| 2.8   | S Sy    | stem Board Transmitter Preset Test                                            | 23 |

| 2     | 2.8.1   | Starting Configuration                                                        | 23 |

| 2     | 2.8.2   | System Board Transmitter Preset Test for 8.0 GT/s                             | 23 |

| 2     | 2.8.3   | System Board Transmitter Preset Test for 16.0 GT/s                            | 24 |

| 2.9   | ) Sy    | stem Board Transmitter Link Equalization Response Test                        | 25 |

| 2     | 2.9.1   | Starting Configuration                                                        | 25 |

| 2     | 2.9.2   | System Board Transmitter Link Equalization Response Test for 8.0 GT/s         | 25 |

| 2     | 2.9.3   | System Board Transmitter Link Equalization Response Test for 16.0 GT/s        | 26 |

| 2.1   | 0 Sy    | stem Lane Margining at 16 GT/s                                                | 27 |

|       |         |                                                                               |    |

|       |         | Architecture PHY Test Specification                                           |    |

| Revis | ion 4.0 | ), Version 0.7                                                                | 3  |

### PCI Express Architecture PHY Test Specification

Revision 4.0, Version 0.7

November 8, 2018

| 2.11 Add | d-in Card Receiver Link Equalization Test                         | 28 |

|----------|-------------------------------------------------------------------|----|

| 2.11.1   | Starting Configuration, Overview of Calibration Steps at 8.0 GT/s | 28 |

| 2.11.2   | Overview of Calibration Steps at 16.0 GT/s                        | 30 |

| 2.11.3   | Add-in Card Receiver Link Equalization Test for 8.0 GT/s          | 34 |

| 2.11.4   | Add-in Card Receiver Link Equalization Test for 16.0 GT/s         | 34 |

| 2.12 Sys | stem Receiver Link Equalization Test                              | 35 |

| 2.12.1   | Starting Configuration, Overview of Calibration Steps at 8.0 GT/s | 35 |

| 2.12.2   | Overview of Calibration Steps at 16.0 GT/s                        | 35 |

| 2.12.3   | System Board Receiver Link Equalization                           | 35 |

| 2.12.4   | System Board Receiver Link Equalization Test for 16.0 GT/s        | 36 |

|          | Add-in Card PLL Bandwidth                                         |    |

| 2.12.6   | Starting Configuration                                            | 37 |

| 2.12.7   | Overview of Test Steps                                            | 37 |

| 2.13 Add | d-in Card PCB Impedance (informative)                             | 38 |

| 2.14 Sys | stem Board PCB Impedance (Informative)                            | 38 |

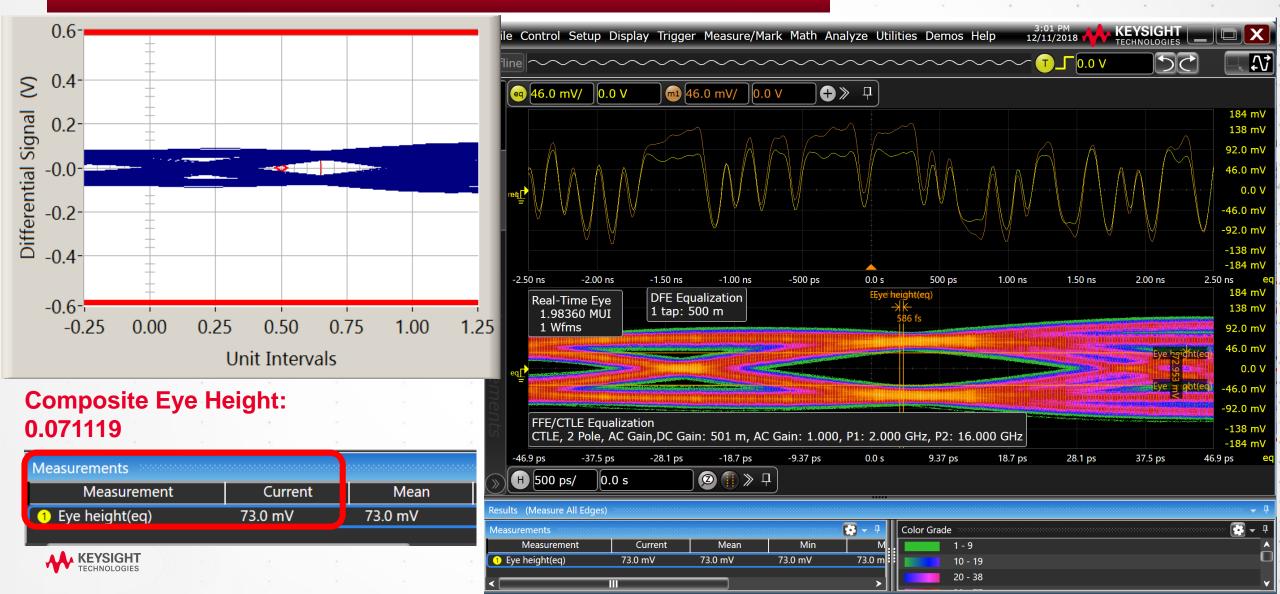

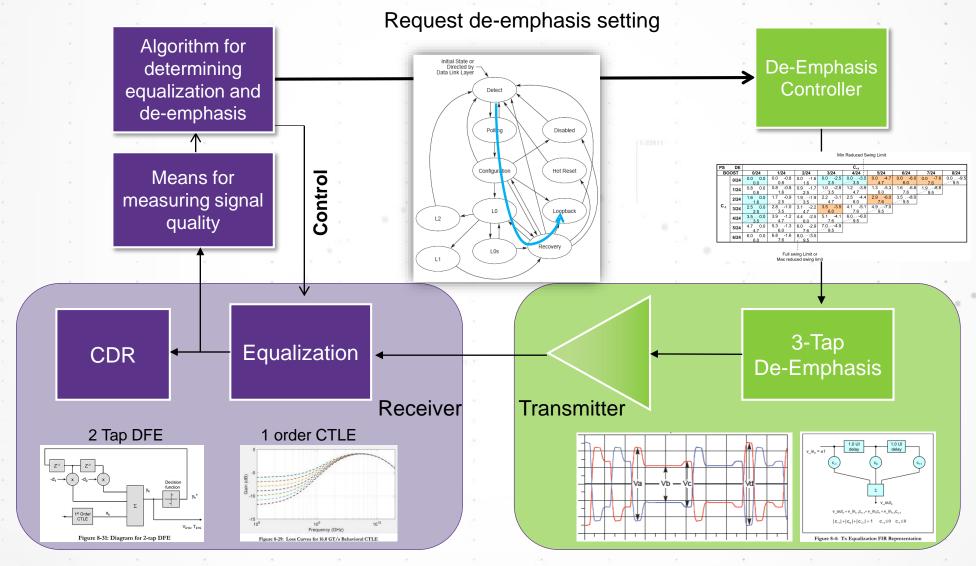

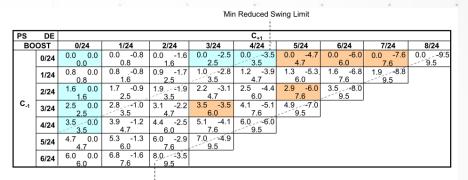

# PCIe Tx EQ De-Emphasis and Rx EQ Equalization

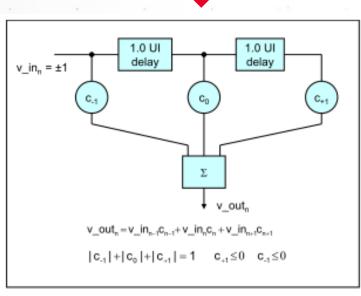

# Reference Tx EQ: 3- Taps FIR, Presets and Cursors

Note 2.

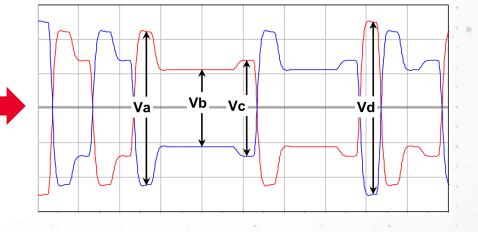

Vc/Vd Preshoot De-emphasis c-1 Va/Vd Vb/Vd 0.000 0.000 1.000 1.000 1.000 P1  $-3.5 \pm 1 \, dB$ 0.000 -0.1671.000 0.668 0.668 P0 0.0 -6.0 ± 1.5 dB 0.000 -0.250 1.000 0.500 0.500  $3.5 \pm 1 \, dB$ 0.0 -0.166 0.000 0.668 0.668 1.000 P8  $3.5 \pm 1 \, dB$ -3.5 ± 1 dB 0.750 -0.125-0.1250.750 0.500 P7  $3.5 \pm 1 dB$ -6.0 ± 1.5 dB -0.100 -0.200 0.800 0.400 0.600 P5 1.9 ± 1 dB 0.0 -0.100 0.000 0.800 0.800 1.000  $2.5 \pm 1 \, dB$ -0.1250.000 0.750 0.750 1.000 P3 -2.5 ± 1 dB 0.000 -0.125 1.000 0.750 0.750 P2 0.000 0.600 0.0 -4.4 ± 1.5 dB -0.200 1.000 0.600

Note 2.

1.000

Note 2.

0.000

Table 8-1. Tx Preset Ratios and Corresponding Coefficient Values

Full swing Limit or Max reduced swing limit

Figure 8-4: Tx Equalization FIR Representation

P10

0.0

Note 2.

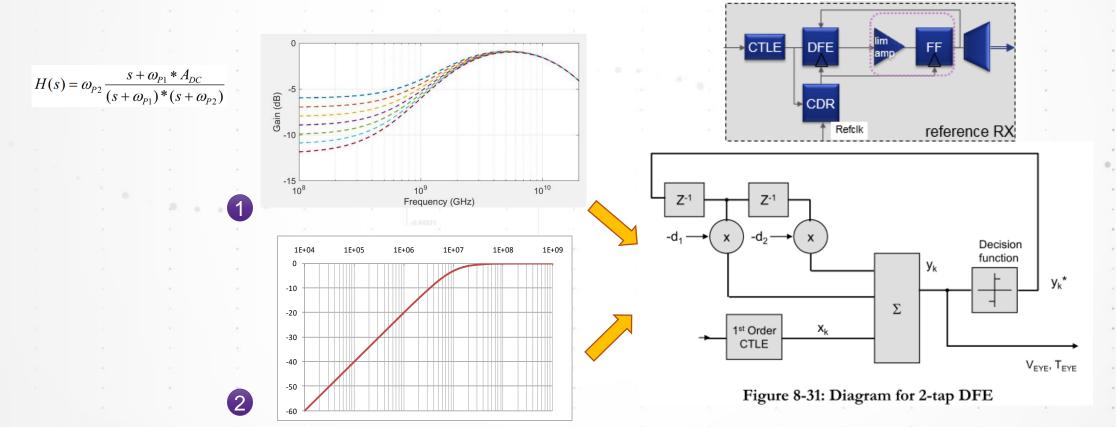

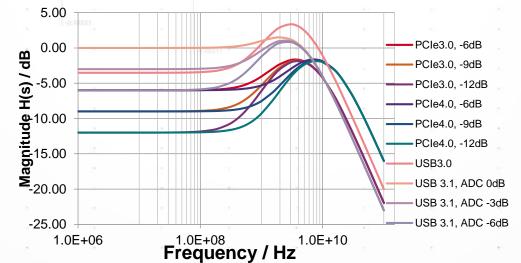

### Reference Rx EQ: CTLE + DFE

### CTLE Should Be Static Setup or Adaptive ?

1st order CTLE with seven different "DC-attenuation" settings peaking at 8 GHz 2 tap DFE with a limit for d1 of +/- 20mV

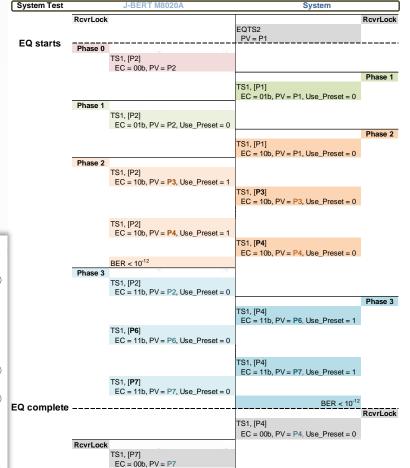

# **Dynamic Link Equalization Handshake 16G**

**DOWNSTREAM PORT**

J-BERT M8020A

### The Four Phases Of The Link Equalization Protocol

Add-In Card

AIC Test

#### Phase 0:

- 2.5 Gb/s

- Downstream port tells upstream port which initial preset to use after the speed change will have been done.

#### Phase 1:

- 8 Gb/s

- · Link partners settle on 8 GT/s speed.

- Exchange FS/LF values.

#### Phase 2:

- 8 Gb/s

- Add-in Card sets up the deemphasis of the System Board's transmitter.

#### Phase 3:

- 8 Gb/s

- System Board sets up the deemphasis of the Add-in Card's transmitter.

#### IF SUCCESSFUL

#### Phase 0:

- 8 Gb/s

- Downstream port tells upstream port which initial preset to use after the speed change will have been done.

#### Phase 1:

- 16 Gb/s

- Link partners settle on 16 GT/s speed.

- Exchange FS/LF values.

#### Phase 2:

- 16 Gb/s

- Add-in Card sets up the deemphasis of the System Board's transmitter.

#### Phase 3:

- 16 Gb/s

- System Board sets up the deemphasis of the Add-in Card's transmitter.

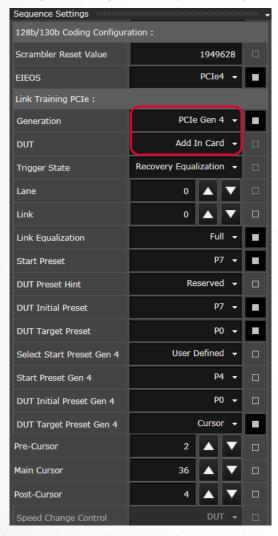

# Tx/Rx Link Equalization Testing

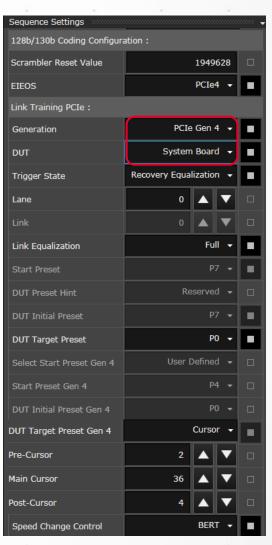

### LTSSM SETUP - PCIE 16GT/S

- EIEOS needs to be set to PCIe3 for PCI Express Base Specification 4.0 rev 0.5. But for PCIe Base Specification 4.0 rev 0.7 and higher it needs to be set PCIe4!

- Generation needs to be set to PCIe Gen 4

- Select DUT type:

- Any endpoint device → Add In Card

- Any root complex device → System Board

- Two sets of phase 0 through phase 3 parameters

- 2.5GT/s to 8GT/s

- DUT Target Preset can be presets only

- 8GT/s to 16GT/s

- DUT Target Preset 4 can be presets or coefficients

- Speed Change Control:

- While the root complex usually is responsible for initiating the speed change, most root complex today need the RX test equipment to take control of the speed change.

# J-BERT M8020A Setup – PCle 4.0

# LTSSM Log – CPU example

Link Training Logging for M1.DataOut1 at 12/05/2018 11:55:20

| State                   | Execution | on Time Transfer | Rate      |  |

|-------------------------|-----------|------------------|-----------|--|

| Detect.Active           | 1.048     | 64 ms 2.5 G      | T/s       |  |

| Polling.Active          | 2.257     | 92 ms 2.5 G      | T/s       |  |

| Polling.Configuration   |           | 22.94616 ms      | 2.5 GT/s  |  |

| Configuration.Linkwidth |           | 528 ns           | 2.5 GT/s  |  |

| Configuration.Linkwidth | .Accept   | 22.96 us         | 2.5 GT/s  |  |

| Configuration.Lanenum   | .Wait     | 2.16 us          | 2.5 GT/s  |  |

| Configuration.Lanenum   | .Accept   | 496 ns           | 2.5 GT/s  |  |

| Configuration.Complete  |           | 1.36 us          | 2.5 GT/s  |  |

| Configuration.ldle      |           | 1.856 us         | 2.5 GT/s  |  |

| L0                      |           | 336 ns           | 2.5 GT/s  |  |

| Recovery.RcvrLock       |           | 4.848 us         | 2.5 GT/s  |  |

| Recovery.RcvrCfg        |           | 2.496 us         | 2.5 GT/s  |  |

| Recovery.Speed          |           | 7.616 us         | 2.5 GT/s  |  |

| Recovery.RcvrLock       |           | 448 ns           | 8.0 GT/s  |  |

| Recovery.Equalization.F | hase0     | 1.074304 ms      | 8.0 GT/s  |  |

| Recovery.Equalization.F | Phase1    | 906.832 us       | 8.0 GT/s  |  |

| Recovery.Equalization.F | Phase2    | 1.728 us         | 8.0 GT/s  |  |

| Recovery.Equalization.F | Phase3    | 10.050416 ms     | 8.0 GT/s  |  |

| Recovery.RcvrLock       |           | 432 ns           | 8.0 GT/s  |  |

| Recovery.RcvrCfg        |           | 1.568 us         | 8.0 GT/s  |  |

| Recovery.ldle           | 432       | ns 8.0 G         | T/s       |  |

| LO                      | 336       | ns 8.0 G         | T/s       |  |

| Recovery.RcvrLock       |           | 3.328 us         | 8.0 GT/s  |  |

| Recovery.RcvrCfg        |           | 816 ns           | 8.0 GT/s  |  |

| Recovery.Speed          |           | 8.96 us          | 8.0 GT/s  |  |

| Recovery.RcvrLock       |           | 448 ns           | 16.0 GT/s |  |

| Recovery.Equalization.F | hase0     | 141.6 us         | 16.0 GT/s |  |

| Recovery.Equalization.F | Phase1    | 629.856 us       | 16.0 GT/s |  |

| Recovery.Equalization.F | hase2     | 1.456 us         | 16.0 GT/s |  |

| Recovery.Equalization.F | Phase3    | 6.97888 ms       | 16.0 GT/s |  |

| Recovery.RcvrLock       |           | 304 ns           | 16.0 GT/s |  |

| Recovery.RcvrCfg        |           | 1.424 us         | 16.0 GT/s |  |

| Recovery.ldle           |           | 112 ns           | 16.0 GT/s |  |

| Loopback.Entry          |           | 2.16 us          | 16.0 GT/s |  |

| Loopback.Active         |           | - 16.0 G         | T/s       |  |

### Change Requests to BERT

| Accept       | Speed | Preset | PreCursor | MainCursor | PostCursor | <b>FullSwing</b> |  |

|--------------|-------|--------|-----------|------------|------------|------------------|--|

| LowFrequency |       |        |           |            |            |                  |  |

| True         | Gen3  | P7     | -         |            | -          | 24               |  |

| True         | Gen3  | PØ     |           |            |            | 24               |  |

| True         | Gen3  | P1     | -         |            | -          | 24               |  |

| True         | Gen3  | P2     |           |            |            | 24               |  |

| True         | Gen3  | P3     | -         |            | -          | 24               |  |

| True         | Gen3  | P4     | -         |            | -          | 24               |  |

| True         | Gen3  | P5     | -         |            | -          | 24               |  |

| True         | Gen3  | P6     |           |            |            | 24               |  |

| True         | Gen3  | P7     | -         |            | -          | 24               |  |

| True         | Gen3  | P8     | -         |            |            | 24               |  |

| True         | Gen3  | P9     |           |            |            | 24               |  |

| True -       | Gen3  | P6     | -         |            |            | 24               |  |

| True         | Gen3  | P7     |           |            |            | 24               |  |

| True         | Gen4  | P0     |           |            |            | 24               |  |

| True         | Gen4  | P1     |           |            |            | 24               |  |

| True         | Gen4  | P2     |           |            |            | 24               |  |

| True         | Gen4  | P3     |           |            |            | 24               |  |

| True         | Gen4  | P4     |           |            |            | 24               |  |

| True         | Gen4  | P5     |           |            |            | 24               |  |

| True         | Gen4  | P6     | -         |            |            | 24               |  |

| True         | Gen4  | P7     |           |            |            | 24               |  |

| True         | Gen4  | P8     | -         |            |            | 24               |  |

| True         | Gen4  | P9     |           |            |            | 24               |  |

| True •       | Gen4  | P7     |           |            |            | 24               |  |

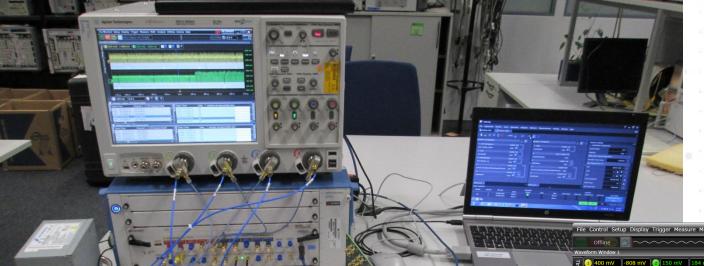

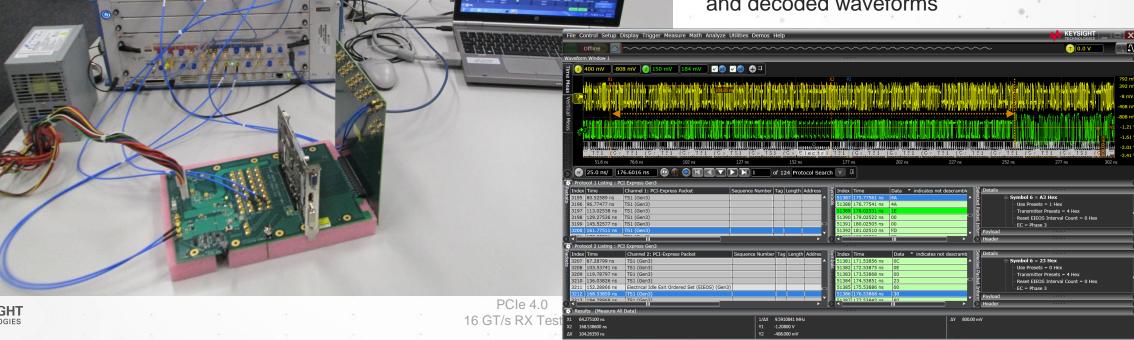

# Tx Link Equalization Testing for PCIe 3.0/4.0

Tests 2.3 and 2.4 – Add-in Card Transmitter Initial TX EQ test and

Link Equalization Response Test Test Setup

J-BERT M8020A is used to train the device and issue a trigger to the scope allowing to capture phase 3

J-BERT TX signal as well as DUT TX signals are split and captured by the scope

The common timing reference allows for timing measurements on the captured and decoded waveforms

# Tx Link Equalization Testing for PCIe 3.0

### Test 2.4 – Example Test Result Report

Show all results

Show only selected

Print

L0\_Cal\_8GTps\_EQ\_Cust\_Preset

L0\_Cal\_8GTps\_RJ

L0\_Cal\_8GTps\_SJ

L0\_Cal\_8GTps\_CBB3\_DM\_SI

L0\_Cal\_8GTps\_CBB3\_Eye\_Height

L0\_Cal\_8GTps\_CBB3\_Eye\_Width

L0\_Cal\_8GTps\_CBB3\_Comp\_Eye

L0\_Rx\_8GTps\_CBB3\_DeEmph\_Scan

L0\_Rx\_8GTps\_CBB3\_PreSh\_Scan

L0 Rx 8GTps CBB3 PreComp 2.8

L0\_Rx\_8GTps\_CBB3\_Comp\_2.8

L0\_EqRx\_8GTps\_CBB3\_Com\_2.10

L0\_Tx\_8GTps\_EQ\_2\_3

L0\_Tx\_8GTps\_EQ\_Comp\_2\_4

Use Power Switch Automation Power Switch Channel Number

Power Cycle Off On Duration Power Cycle Settling Time Power Cycle max. Retries

for LB Training

True

7 s

. .

3

| Result | DUT Target<br>Preset | Electrical<br>response<br>time [ns] | Protocol<br>response<br>time [ns] | Pre-<br>Shoot<br>[dB] | Min<br>Spec<br>PS<br>[dB] | Max<br>Spec<br>PS<br>[dB] | De-<br>Emphasis<br>[dB] | Min<br>Spec<br>DE<br>[dB] | Max<br>Spec<br>DE<br>[dB] | Comment                            |

|--------|----------------------|-------------------------------------|-----------------------------------|-----------------------|---------------------------|---------------------------|-------------------------|---------------------------|---------------------------|------------------------------------|

| pass   | P0                   | 129.87                              | 125.25                            | 0.00                  | 0.00                      | 0.00                      | -6.03                   | -7.50                     | -4.50                     | DUT reported cursors:<br>(0,45,15) |

| pass   | P1                   | 125.12                              | 136.12                            | 0.00                  | 0.00                      | 0.00                      | -3.54                   | -4.50                     | -2.50                     | DUT reported cursors:<br>(0,50,10) |

| pass   | P2                   | 126.25                              | 125.87                            | 0.00                  | 0.00                      | 0.00                      | -4.45                   | -5.90                     | -2.90                     | DUT reported cursors:<br>(0,48,12) |

| pass   | P3                   | 131.87                              | 124.62                            | 0.00                  | 0.00                      | 0.00                      | -2.71                   | -3.50                     | -1.50                     | DUT reported cursors:<br>(0,52,8)  |

| pass   | P4                   | 132.25                              | 121.62                            | 0.00                  | 0.00                      | 0.00                      | 0.00                    | 0.00                      | 0.00                      | DUT reported cursors:<br>(0,60,0)  |

| pass   | P5                   | 126.37                              | 130.37                            | 1.93                  | 0.90                      | 2.90                      | 0.00                    | 0.00                      | 0.00                      | DUT reported cursors:<br>(6,54,0)  |

| pass   | P6                   | 128.50                              | 132.00                            | 2.69                  | 1.50                      | 3.50                      | 0.00                    | 0.00                      | 0.00                      | DUT reported cursors:<br>(8,52,0)  |

| pass   | P7                   | 134.50                              | 132.37                            | 3.51                  | 2.50                      | 4.50                      | -6.03                   | -7.50                     | -4.50                     | DUT reported cursors:<br>(6,42,12) |

| pass   | P8                   | 131.12                              | 121.62                            | 3.91                  | 2.50                      | 4.50                      | -3.92                   | -4.50                     | -2.50                     | DUT reported cursors:<br>(8,44,8)  |

| pass   | P9                   | 130.75                              | 128.12                            | 3.50                  | 2.50                      | 4.50                      | 0.00                    | 0.00                      | 0.00                      | DUT reported cursors:<br>(10,50,0) |

| pass   | P0' (0,45,15)        | 127.12                              | 128.25                            | 0.00                  | 0.00                      | 0.00                      | -6.03                   | -7.50                     | -4.50                     |                                    |

| pass   | P1' (0,50,10)        | 127.12                              | 127.75                            | 0.00                  | 0.00                      | 0.00                      | -3.54                   | -4.50                     | -2.50                     |                                    |

| pass   | P2' (0,48,12)        | 126.00                              | 124.12                            | 0.00                  | 0.00                      | 0.00                      | -4.46                   | -5.90                     | -2.90                     |                                    |

| pass   | P3' (0,52,8)         | 142.12                              | 120.12                            | 0.00                  | 0.00                      | 0.00                      | -2.70                   | -3.50                     | -1.50                     |                                    |

| pass   | P4' (0,60,0)         | 127.00                              | 126.87                            | 0.00                  | 0.00                      | 0.00                      | 0.00                    | 0.00                      | 0.00                      |                                    |

| pass   | P5' (6,54,0)         | 130.50                              | 121.37                            | 1.93                  | 0.90                      | 2.90                      | 0.00                    | 0.00                      | 0.00                      |                                    |

| pass   | P6' (8,52,0)         | 127.25                              | 121.37                            | 2.68                  | 1.50                      | 3.50                      | 0.00                    | 0.00                      | 0.00                      |                                    |

| pass   | P7' (6,42,12)        | 125.37                              | 128.12                            | 3.50                  | 2.50                      | 4.50                      | -6.03                   | -7.50                     | -4.50                     |                                    |

| pass   | P8' (8,44,8)         | 123.75                              | 123.37                            | 3.91                  | 2.50                      | 4.50                      | -3.93                   | -4.50                     | -2.50                     |                                    |

| pass   | P9' (10,50,0)        | 133.75                              | 119.87                            | 3.52                  | 2.50                      | 4.50                      | 0.00                    | 0.00                      | 0.00                      |                                    |

# Tx Link Equalization Testing for PCIe 3.0

Tests 2.7 System Board Transmitter Link Equalization Response Test - Test Setup

J-BERT M8020A is used to train the device and issue a trigger to the scope allowing to capture phase 2

J-BERT TX signal as well as DUT TX signals are split and captured by the scope

J-BERT M8020A is synchronized to the system by the system's 100MHz clock

It is not necessary to turn off SSC on the system side

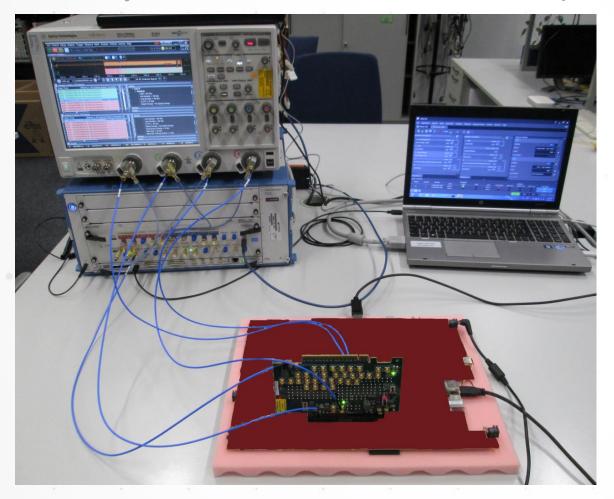

# Rx Link Equalization Testing for PCIe 3.0

Tests 2.10 – Add-in Card Receiver Link Equalization Test - Test Setup

J-BERT M8020A is used to train the device through L0 and recovery into loopback

Phase 2 and 3 are performed and the AIC optimizes J-BERT TX to the actual stress signal

J-BERT checks the looped signal for the BER

Very clean setup since no additional instruments or repeaters are required

# Rx Link Equalization Testing for PCIe 3.0

Tests 2.11 System Receiver Link Equalization Test – Test Setup

J-BERT is running on the system's 100MHz reference clock

J-BERT M8020A is used to train the system through L0 and recovery into loopback

Phase 3 are performed and the System optimizes J-BERT TX to the actual stress signal

J-BERT checks the looped signal for the BER

Very clean setup since no additional instruments or repeaters are required

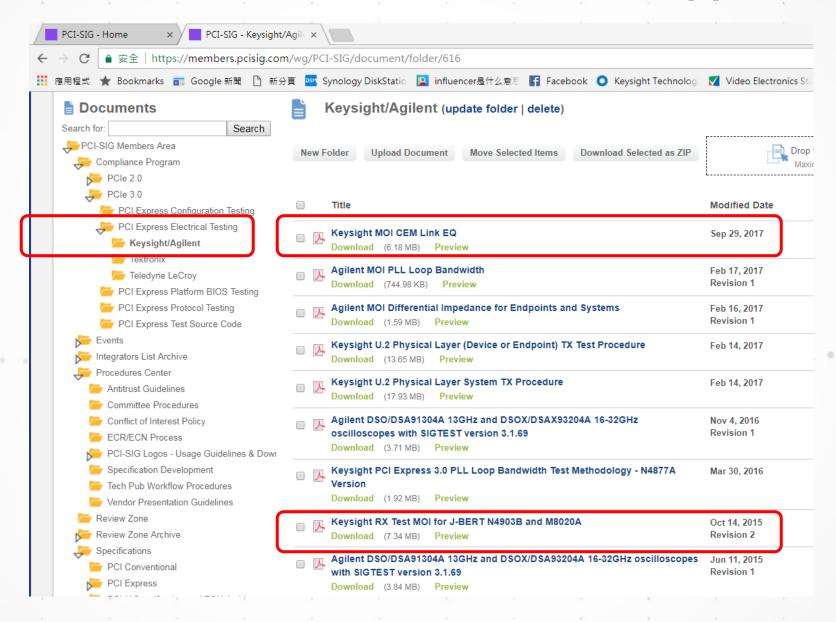

### PCle3.0 Rx and CEM LinkEQ Test Gold Suites approval by PCISIG

### **PCIe 4.0 Base Receiver Tests**

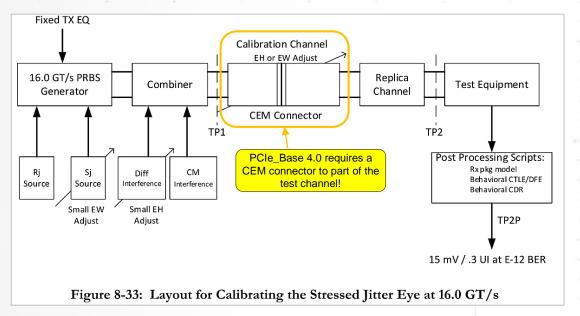

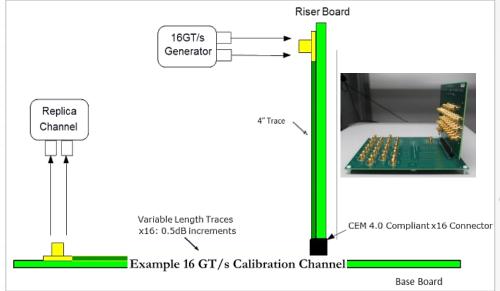

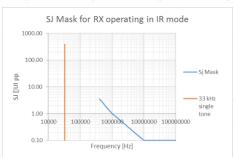

### 16GT/s Base Specification - RX Calibration Channel

- The test channel is the long Rx calibration channel with a total loss of 28.0dB at (Physical channel loss 23dB for RC)

- PCIe 4.0 Base Spec requires a CEM connector to be part of the test channel 8GHz.

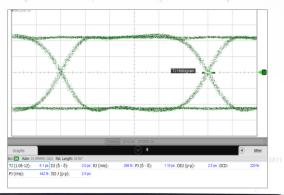

- Stress jitter eye height ≤15mV, Eye width ≤0.3UI, same with CEM spec.

- Channel calibration with preset selection to get as close to target eye height and eye width as possible.

- Compliance eye calibration is done by adjusting DM-SI, SJ or V<sub>diff</sub>.

- DM-SI and CM-SI are calibrated through the channel.

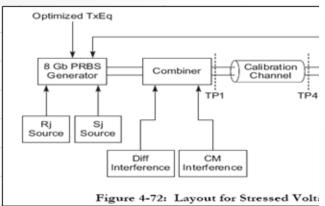

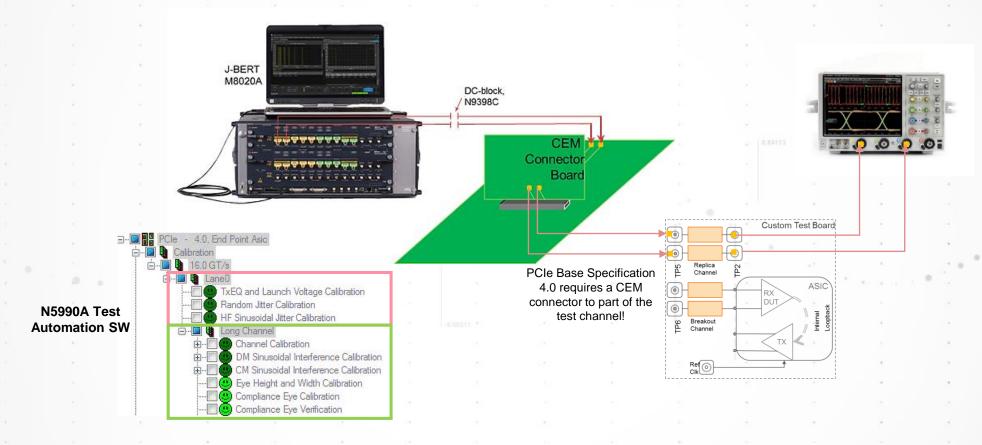

### PCIe 4.0 Base Receiver Tests - Calibration

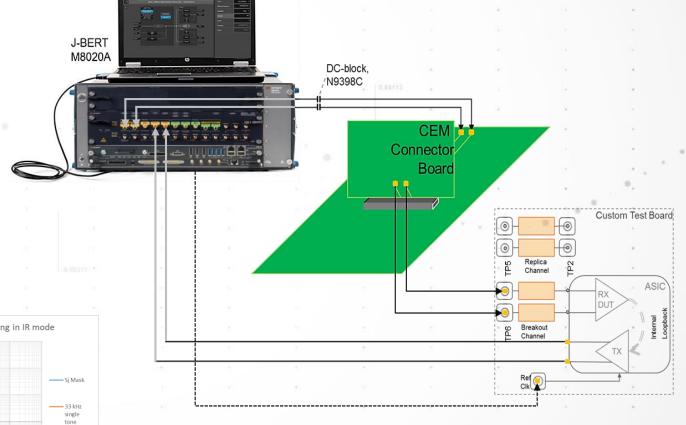

### 16GT/s Base Specification - RX Stress Signal Calibration Setup

- J-BERT M8020A's internal ISI can be used to calibrate channel.

- All other impairments are provided by J-BERT M8020A (RJ, SJ, DMSI, ISI, SSC).

- A built-in reference clock multiplier enables J-BERT M8020A to operate on a DUT's reference clock if required.

### **PCIe 4.0 Base Receiver Tests**

### 16GT/s Base Specification - RX Test Setup

- PCIe 4.0 Base Spec requires a CEM connector to be part of the test channel!

- All other impairments are provided by J-BERT M8020A

- A built-in reference clock multiplier enables J-BERT M8020A to operate on a DUT's reference clock if required

- No ref clock connection in case of IR / SRIS

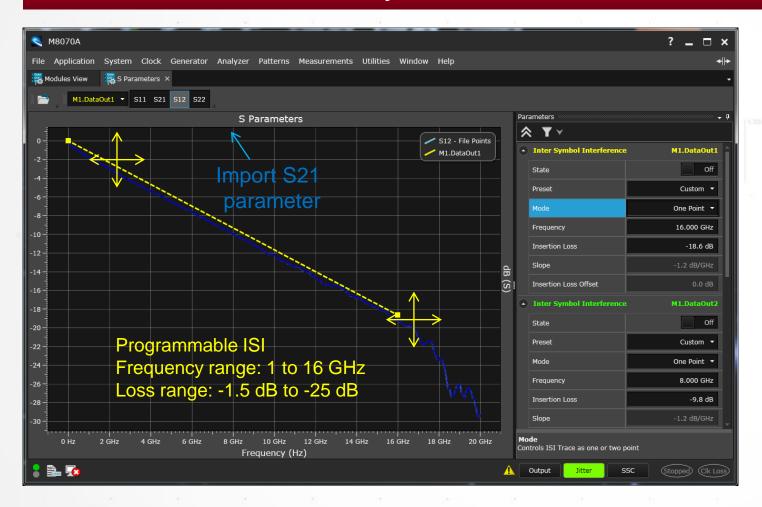

### **Emulating Loss with J-BERT M8020A**

### **DATA OUTPUT - Internally Generated ISI**

M8020A J-BERT

# Integrated ISI for streamlined RX Test Setups and accurate Results:

- Adjustable loss and frequency up to 25dB @16GHz

- Import of S-parameters

- Multiple channels

- Programmable

- Upgradeable option

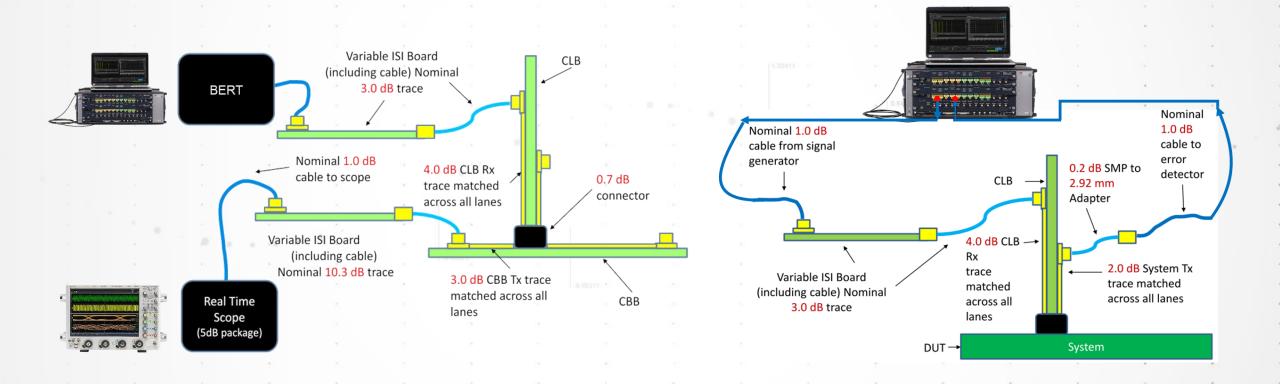

### **PCIe 4.0 CEM Receiver Tests**

### 16GT/s CEM Specification - System RX Calibration and Test

Note: This RX test proposal utilizes an external variable ISI board to ensure consistent insertion loss of the test setup.

### **PCIe 4.0 CEM Receiver Tests**

### 16GT/s CEM Specification - AIC RX Calibration and Test

Note: This RX test proposal utilizes an external variable ISI board to ensure consistent insertion loss of the test setup.

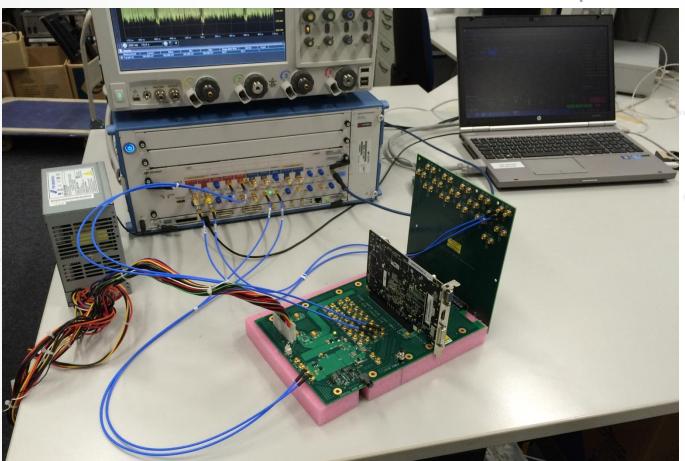

# PCIe 4.0 CEM Test Setup

### Calibration Setup Example For 16GT/s RX

- CBB 4.0 as well as CLB 4.0 need to be combined with ISI trace boards

- CEM calibration procedure is very similar to base spec calibration but SIGTEST instead of SEASIM is mandatory

- J-BERT M8020A successfully tested most of the 16 GT/s AICs and systems at PCIe WS 101

- Many AICs and systems could be trained to loopback using the new LTSSM

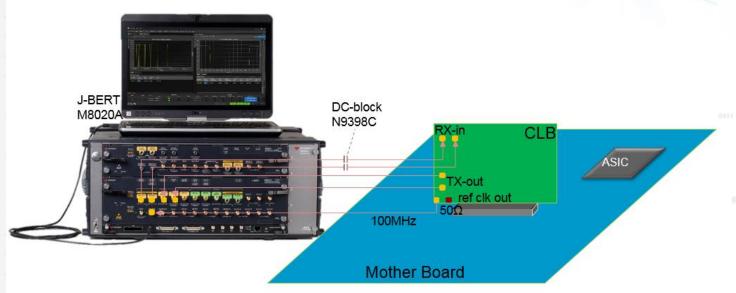

# PCIe 3.0/4.0 RX Test Solution - now

**Latest Generation**

J-BERT

M8020A Support for CC as well as IR End point as well as root complex 2.5 GT/s, 5 GT/s, 8 GT/s and 16 GT/s

ref clk out

### J-BERT M8020A (8-32 Gb/s)

- Interactive Training Function

- Build in Jitter Sources /DMI + CMI source

- · Build in CDR and analyzer equalization

- Build in 8 Tap De-emphasis

- Build Adjustable ISI

- Support fully programmable

Real Time Scope for calibration

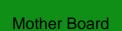

# Key of Successful PCIe Gen4 Rx testing: CTLE & CDR

### BERT ED GET CHALLENGE WITH LONG TRACE

### The Key with Error Free:

No additional loss with integrated CDR

Tx signal after > 10 inches

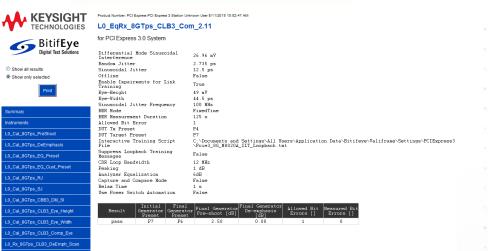

# **Example: System board Gen4 Rx Test Report**

#### BEAUTIFUL TEST REPORT WITH DETAIL INFORMATION

O Show all results

Show only selected

**Print**

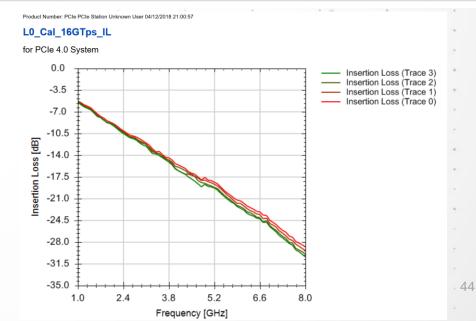

L0 Cal\_16GTps\_IniPres\_EH

L0 Cal 16GTps IniPres EW

L0 Cal 16GTps Chan EH

L0 Cal 16GTps Chan EW

L0 Cal 16GTps FinPres EH

L0 Cal 16GTps FinPres EW

L0 Cal 16GTps PreComp

L0\_Cal\_16GTps\_CompEye

L0\_Rx\_16GTps\_Comp

L0\_EqRx\_16GTps\_Comp\_2.12.2

KEYSIGHT

Product Number: PCIe PCIe Station Unknown User 05/12/2018 12:00:40

#### L0\_EqRx\_16GTps\_Comp\_2.12.2

for PCle 4.0 System

Enable Impairments for Loopback

BER Measurement Duration

Training

BER Mode

| Random Jitter                                | 1 ps     |

|----------------------------------------------|----------|

| Sinusoidal Jitter                            | 10 ps    |

| Differential Mode Sinusoidal<br>Interference | 17 mV    |

| Generator Launch Voltage                     | 800 mV   |

| Offline                                      | False    |

| CLB var. ISI pair                            | 2        |

| Total Channel Loss                           | -29.9 dB |

| Sinusoidal Jitter Frequency                  | 100 MHz  |

| Common Mode Sinusoidal<br>Interference       | 150 mV   |

|                                              |          |

| Allowed Bit Error                 | 1                                 |

|-----------------------------------|-----------------------------------|

| Interactive Training Script File  | C:\ProgramData\BitifEye\ValiFrame |

| Default Link Training Lane Number |                                   |

True

FixedTime

62.5 s

| Default Link Training Lane Number<br>for every Lane | Auto  |

|-----------------------------------------------------|-------|

| Suppress Loopback Training<br>Messages              | False |

| Use Gen3 EIEOS                                      | False |

| DUT Target Preset                                   | P5    |

| DUT Target Preset Gen4                              | P5    |

| Speed Change Control                                | DUT   |

| Drop Link Method                                    | LTSSM |

| Drop Link Method                     | LTSSM           |

|--------------------------------------|-----------------|

| Use CDR                              | True            |

| CDR Loop Bandwidth                   | 20 MHz          |

| Peaking                              | 1 dB            |

| Analyzer Equalization                | -9 dB           |

| Sensitivity                          | High            |

|                                      |                 |

| Polarity                             | Normal          |

| Polarity<br>Capture and Compare Mode | Normal<br>False |

| 1                                    |                 |

| Capture and Compare Mode             | False           |

| Result | Final<br>Generator<br>Preset | Final Generator<br>Pre-shoot [dB] | Final Generator<br>De-emphasis [dB] | Allowed Bit<br>Errors [] | Measured Bit<br>Errors [] |

|--------|------------------------------|-----------------------------------|-------------------------------------|--------------------------|---------------------------|

| pass   | P5                           | 1.90                              | 0.00                                | 1                        | 0                         |

### Agenda

- PCI Express 4.0 Simulation and Case Study

- > PCI Express 4.0 Timeline and 5.0 Roadmap

- > PCI Express 4.0 TX / LTSSM Link EQ / RX Testing

- PCI Express 5.0 Preview

# **PCIe Gen5 Preliminary Goals**

# PCI Express<sup>®</sup> Base Specification Revision 5.0 Version 0.9

### PCIE Base Spec Ver: 0.5

PCI-SIG 18 October 2018

- Signaling rate: 32GT/s NRZ (no PAM4)

- Channel loss target is: -36dB @ 16GHz (Nyquist), Package Loss RC -9dB, EP -4dB

- PCIe 5.0 base specification compliant PHYs must support both common clock and SRIS clocking architectures

- Reference Clock is reduced from 300 ppm to 100 ppm, Phase Jitter: ≤ 250fs RMS

- BER target is 1e-12

- 2<sup>nd</sup> order CTLE and 3-tap DFE for 32GT/s

- TX Presets P0-P10 to remain the same

- Backward compatibility with previous PCIe Gen1/2/3/4

- Same TX Voltage parameters as Gen4

- Same approach for TX and RX testing used for Gen4

- Similar method for TX testing via de-embedding of breakout board traces

- Similar method for calibrating the eye width and eye height as used with PCIe 4.0 (ISI based, fixed RJ)

# PCI Express® 4.0 – Keysight Total Solution

DSA V-series & Z-Series Real-Time Oscilloscopes Automated RX Test software

- Accurate, Efficient

- Comprehensive RX Testing