## Understanding PCB Layout Effects on DC-DC Converters

CHEN, Jason OCT. 2019

Application Engineer

1.02410

### **Challenges in Power Circuit Design**

High switching frequency along with high frequency components in waveform causes unexpected EMI

Prototype circuit explosion due to unexpected surge

High switching frequency and associated surge/ringing causes malfunction

Lack of power circuit simulation tool. Conventional tool may work for low frequency circuit but not for WBG device circuit

## **Traditional Low Speed Design Approach**

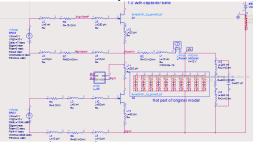

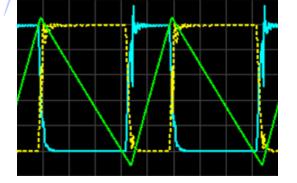

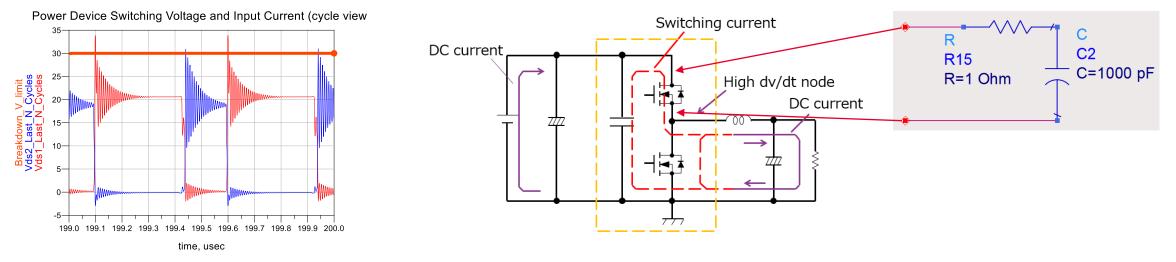

#### PRE-LAYOUT SPICE, THEN "CUT AND TRY"

Pre-layout schematic SPICE simulation: "Best Case" performance

First prototype has some excess ringing. Cut-and-try until "best case" approached

Image courtesy of ST Microelectronics

time, usec

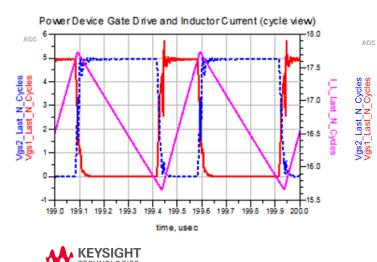

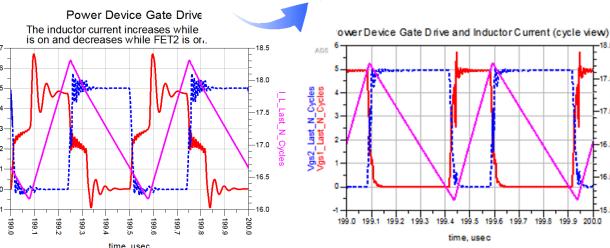

### **Traditional Design Approach Applied to High Speed**

#### PRE-LAYOUT SPICE, THEN "CUT AND TRY"

Pre-layout schematic SPICE simulation: "Best Case" performance

First prototype has destructive failure.

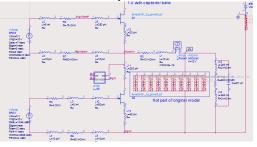

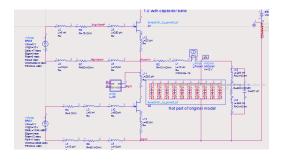

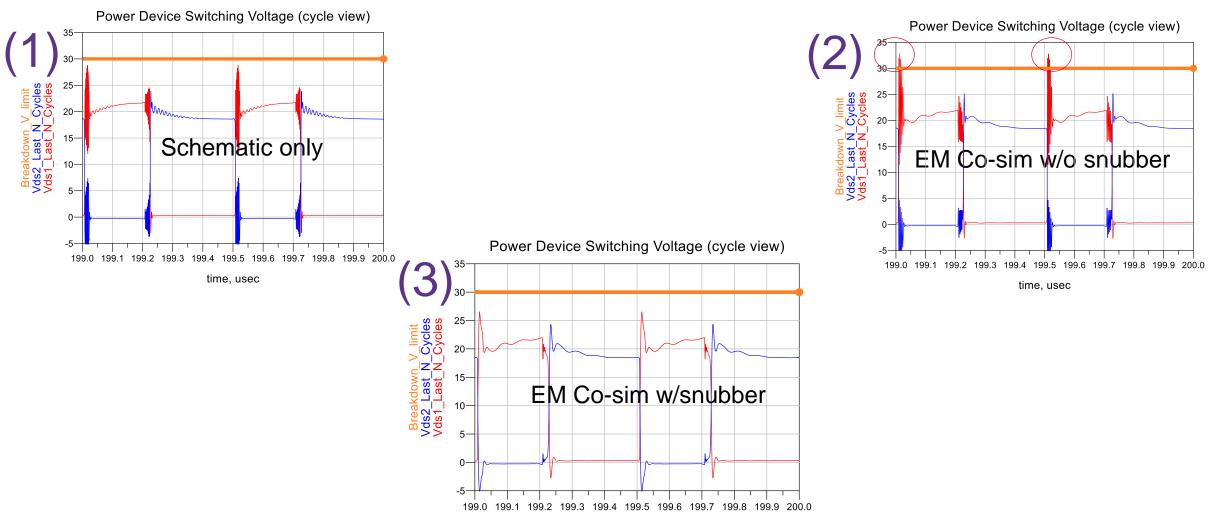

## A New Approach for High Speed Design: ST Case Study

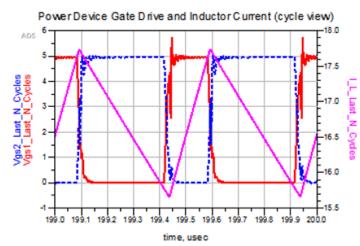

Pre-layout schematic SPICE simulation: "Best Case" performance

#### **New step Post-layout = Integrated EM-circuit co-sim**

First pass success

First "virtual" prototype has some excess ringing. "White box" – probe anywhere - data display – 3D visualization Explore design space until "best case" approached

time, use c

Copyright 2019 Reysight Technologies, Inc.

-16.5

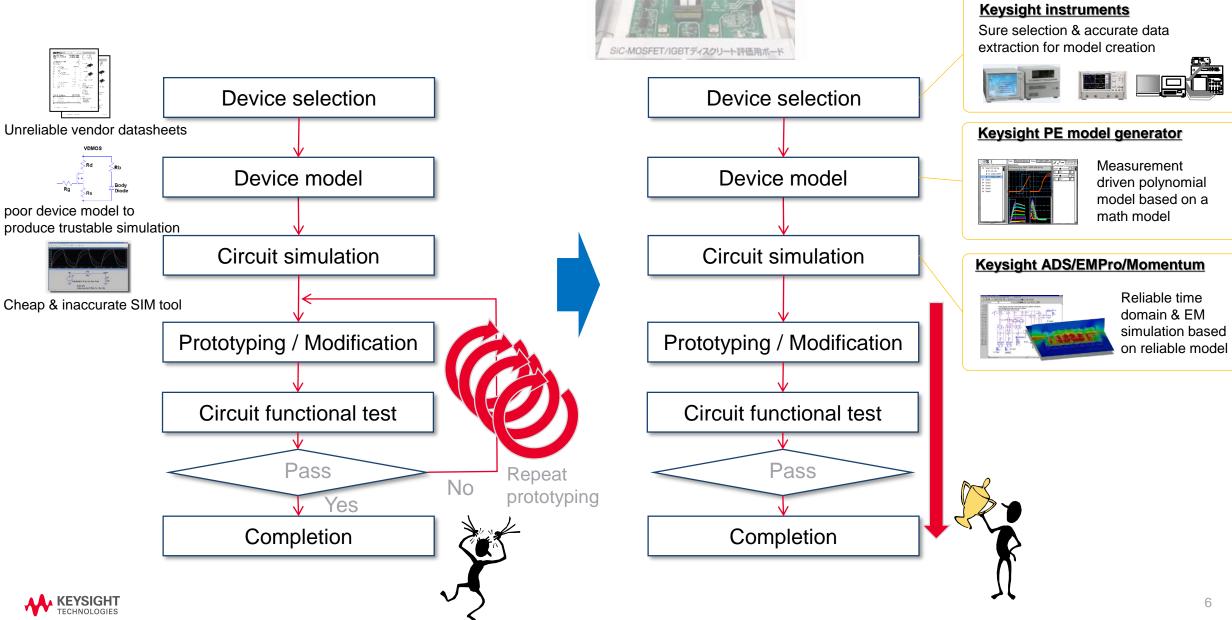

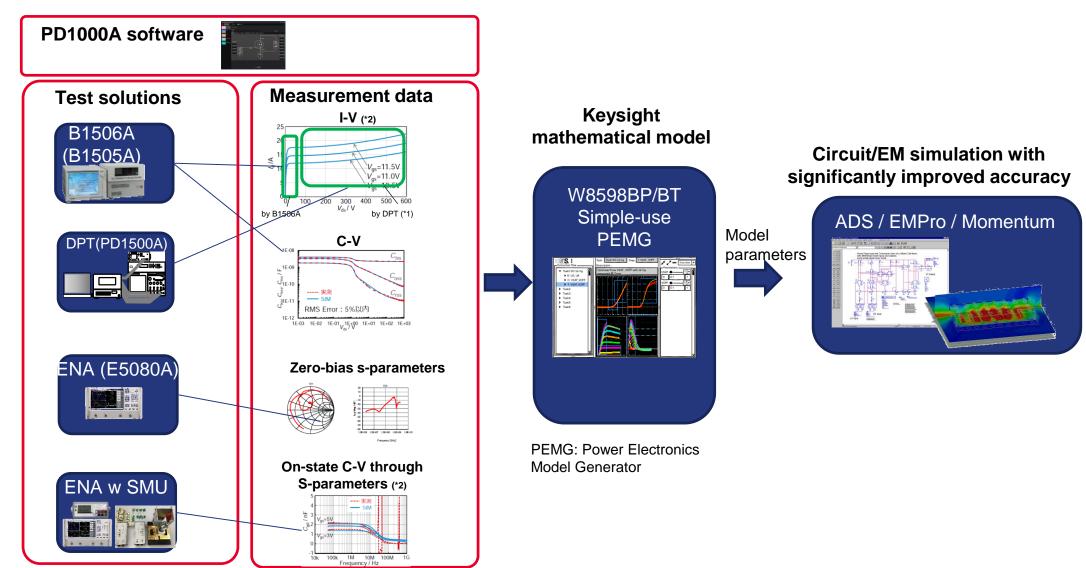

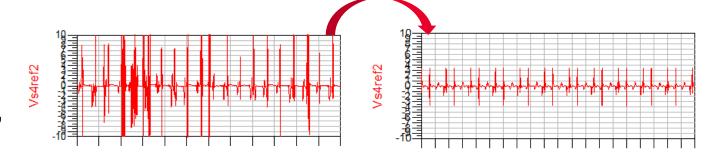

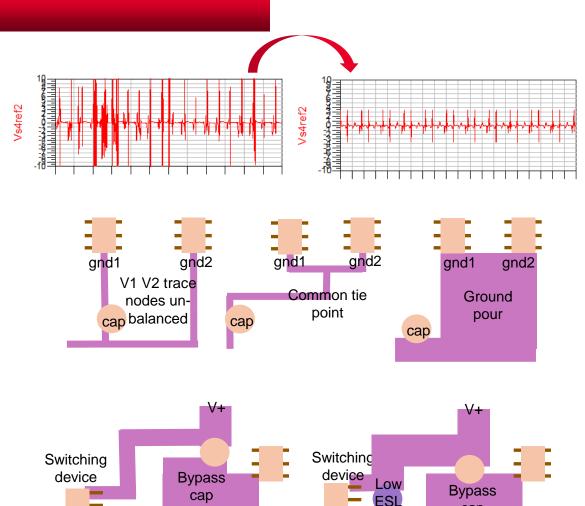

### **Before & After Our Solution**

### **Keysight Solutions for Power Electronics**

KEYSIGHT

### **Physical Parasitic Effects**

CAUSES, IMPACT, REMEDIES

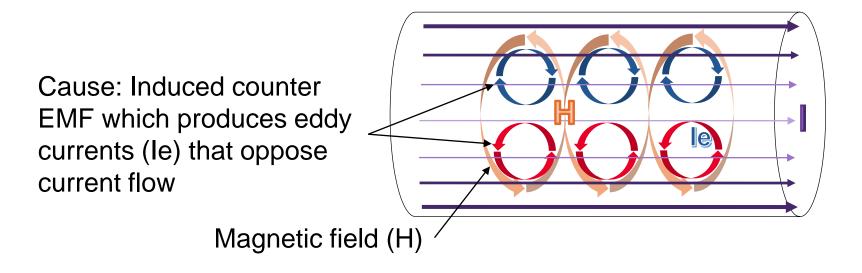

### **Skin Effect**

#### WHAT IS IT?

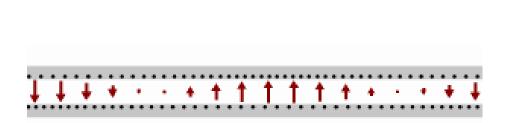

Definition: The characteristic of AC current such that the current density within a conductor is largest near the surface of a conductor, and decreases with greater conductor depth

### **Skin Effect**

#### CHARACTERISTICS

### **Current Density**

Current density J decreases exponentially by the ratio of physical depth/skin depth from the surface current density Js

$J = J_{\rm S} e^{-d/\delta}$

# 63% of current (I) flows within the skin depth

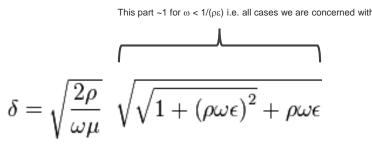

#### Skin Depth Calculation

Skin depth is highly dependent on the angular frequency

ho = resistivity of the conductor

$\omega$  = angular frequency of current =  $2\pi \times$  frequency

$\mu_r$  = relative magnetic permeability of the conductor

$\mu_0$  = the permeability of free space

$\mu = \mu_r \mu_0$

$\epsilon_r$  = relative permittivity of the material

$\epsilon_0$  = the permittivity of free space

$\epsilon = \epsilon_r \epsilon_0$

| Skin Depth vs Frequency |         |      |  |  |

|-------------------------|---------|------|--|--|

| Frequency               | microns | mils |  |  |

| 10 KHz                  | 654     | 25.6 |  |  |

| 100 KHz                 | 207     | 8.15 |  |  |

| 1 MHz                   | 65      | 2.56 |  |  |

| 10 MHz                  | 21      | 0.82 |  |  |

| 100 MHz                 | 7       | 0.26 |  |  |

|                         |         |      |  |  |

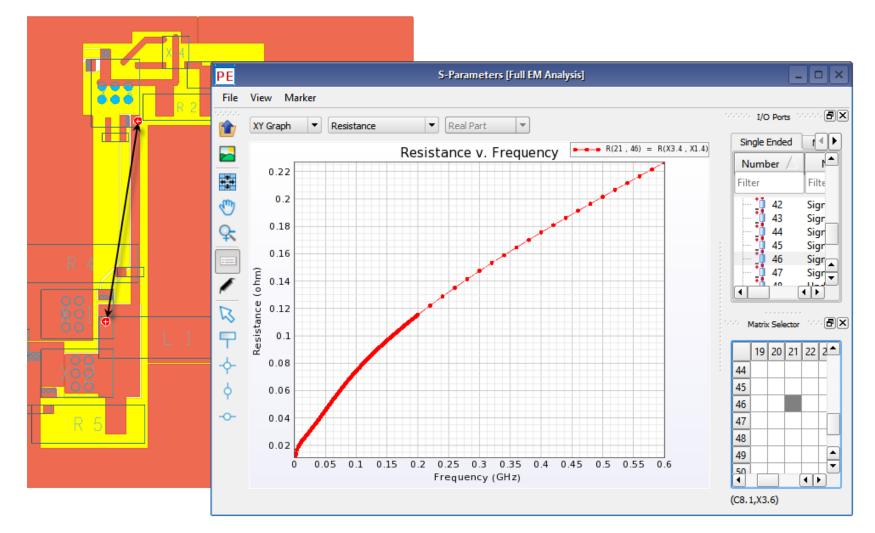

### **Example: Copper Trace in PEPro**

### **Keysight's Unique Capability: Circuit Excitation**

• Like other tools, Keysight's solution shows you have a problem...

...but unlike other tools we show you how to fix it. We have a unique feature called "Circuit excitation" that pinpoints the root cause.

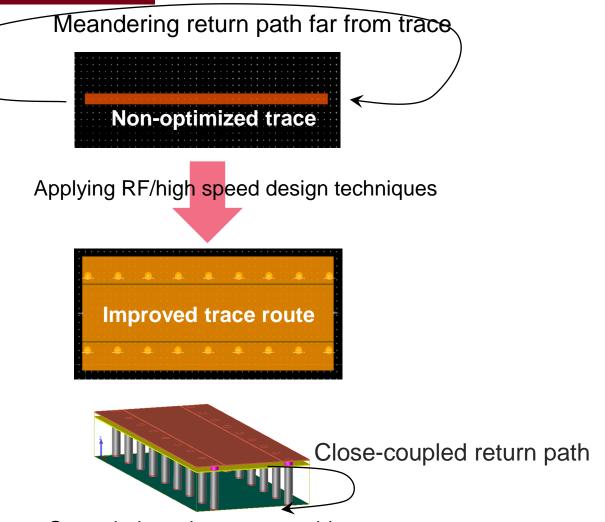

### **Q: How to Make a Trace Less Inductive?**

- 1. Shorten it

- 2. Lower the inductance per unit length...

### **Q: How to Make a Trace Less Inductive Per Unit Length?**

#### A: MAKE IT MORE LIKE A CAPACITOR!

- Fundamental reciprocal relationship between L and C for any trace (transmission line theory):  $L = \frac{1}{v^2 C}$

- ...where v is the (fixed) propagation speed, v:  $v = \frac{c}{\sqrt{\varepsilon_r}}$

- ...where c is the speed of light in vacuum

- $\rightarrow$  If you increase C, L has to come down

- It is easier to think what to do to make a bigger parallel plate capacitance  $C = \frac{c}{l} = \frac{\varepsilon_0 \varepsilon_r w}{d}$  than it is to think what to do to make a smaller inductance

### **Q: How to Make a Trace Less Inductive Per Unit Length?**

#### A: MAKE IT MORE LIKE A CAPACITOR!

• Think of a parallel plate capacitor  $C = \frac{c}{l} = \frac{\varepsilon_0 \varepsilon_r w}{d}$

Make *w* big: Make a skinny trace fatter

Make *d* small: Current flows in loops. Bring the return path closer. Under, over, co-planar or all three.

Grounded co-planar waveguide structure

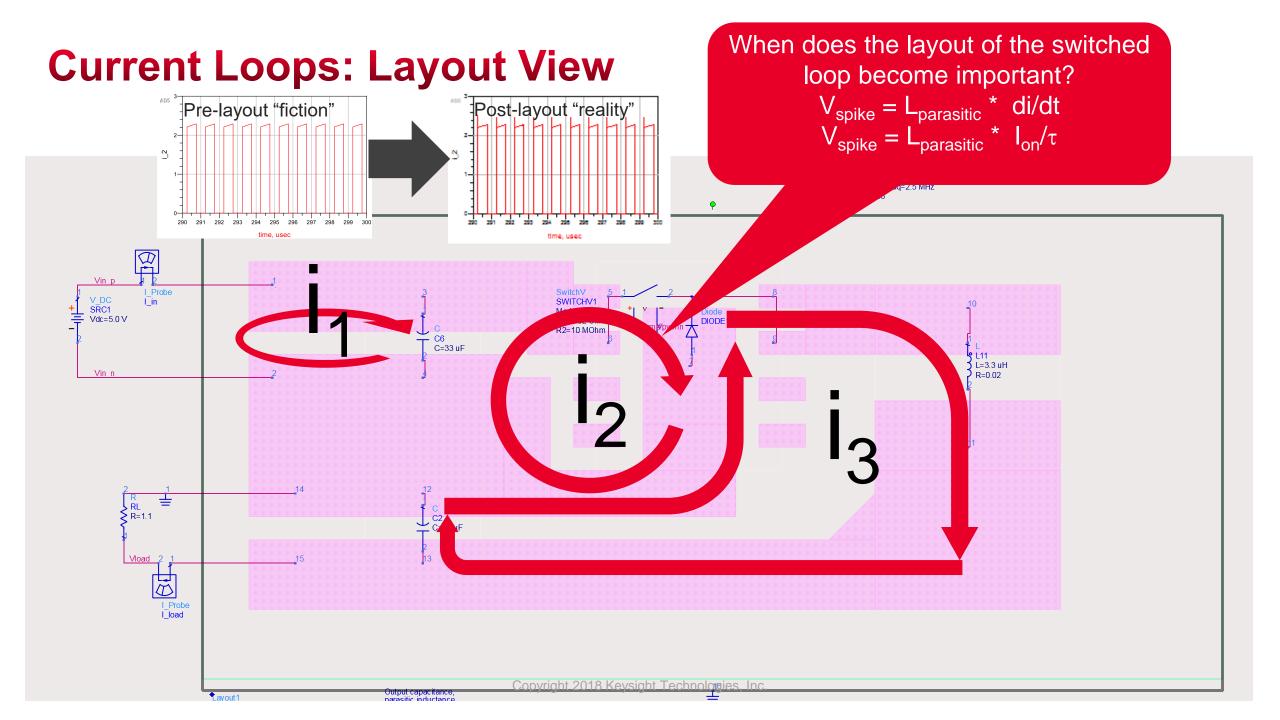

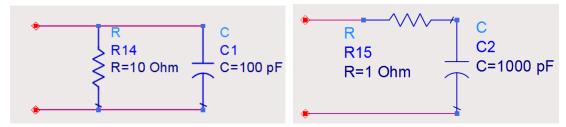

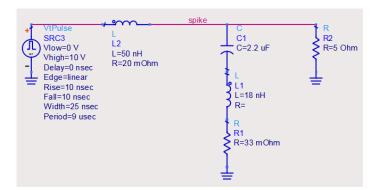

### di/dt Voltage Spike Remedy

#### RC SNUBBERS - USED AS A LAST RESORT

**Definition:** A circuit which reduces spike voltage and parasitic oscillations. Parasitic oscillations occur when the surge voltage impulse excites an LC circuit.

Snubbing circuits are usually placed across high dv/dt switching nodes

RC snubbers always decrease efficiency.

- Rsnub dissipates heat directly

- Csnub stores energy= ½ x C<sub>snub</sub> x V<sup>2</sup> which is dissipated every cycle

### di/dt Voltage Spike Remedy

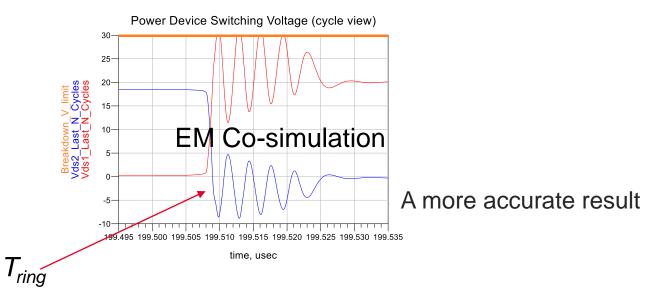

#### RING FREQUENCY DESIGN METHODOLOGY

**Frequency ringing method:** Choose  $R_{snub}$ , determine frequency of ringing, back solve for  $C_{snub}$ .

$C_{snub} = 3 \ x \ T_{ring} / R_{snub}$  $T_{ring}$  can be found by simulation. Use results determined from EM Co-simulation!

Note: There many papers on snubber design e.g. William McMurray, OPTIMUM SNUBBERS FOR POWER SEMICONDUCTORS, IEEE IAS transactions, Vol. IA-8, No. 5, Sept/Oct 1972, pp. 593-600

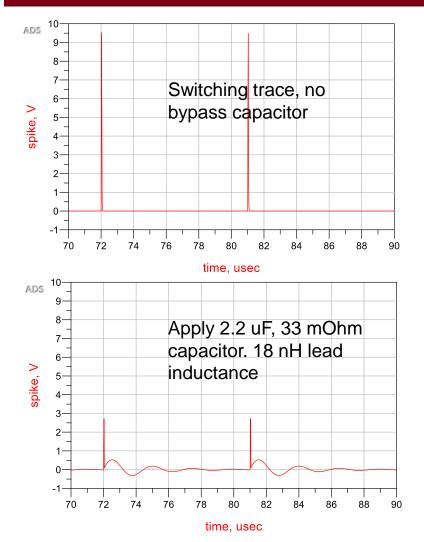

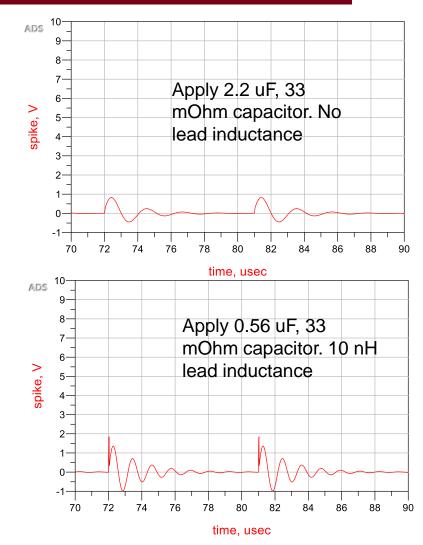

### di/dt Voltage Spike Remedy

#### APPLYING THE RING FREQUENCY DESIGN METHOD

time, usec Controlling Parasitic Effects

### di/dt Voltage Spike Remedy Summary

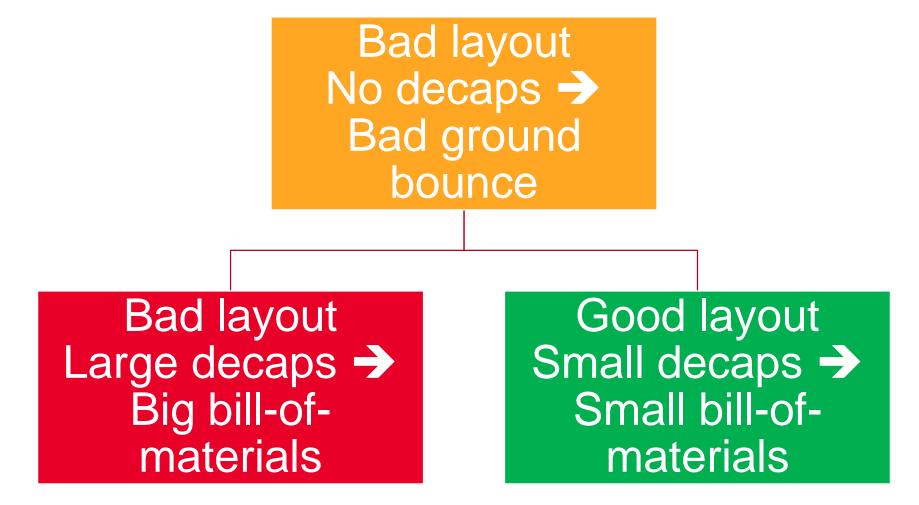

#### TRACE LAYOUT, SNUBBING

#### Trace layout:

Lower L di/dt by widening traces, shrinking route length, increasing capacitance, careful via placement

#### Loading/snubbing:

Resistive/capacitive loads and snubbing circuits can be used to control surge voltage, but sacrifices efficiency

# Don't Add a Snubber Until the Layout is as Good as it Can Be

Bad layout No snubber -> **Bad spiking Bad layout** Good layout Small snubber → Large snubber -> Poor efficiency Good efficiency Small bill-of-materials **Big bill-of-materials**

The "Ground" Myth

"Ground is a place where potatoes and carrots thrive!" Dr. Bruce Archambeault, IBM Distinguished Engineer IEEE Fellow http://web.mst.edu/~jfan/slides/Archambeault2.pdf

**Controlling Parasitic Effects**

### Forget ground, think "return path"

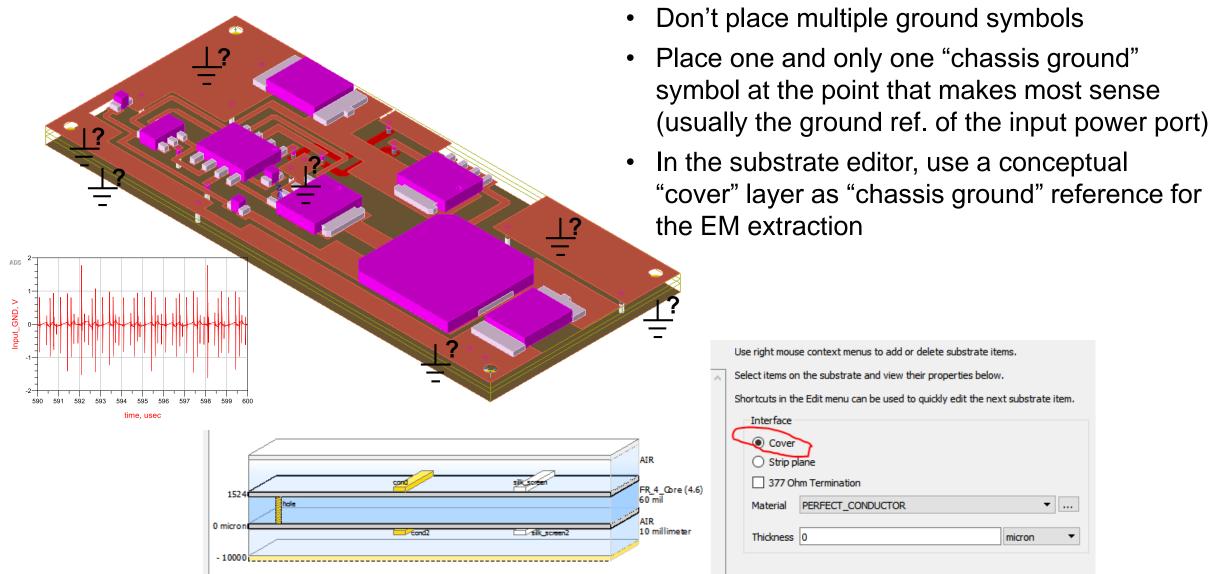

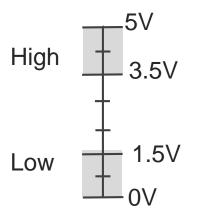

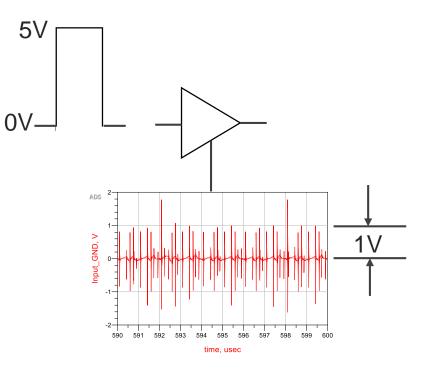

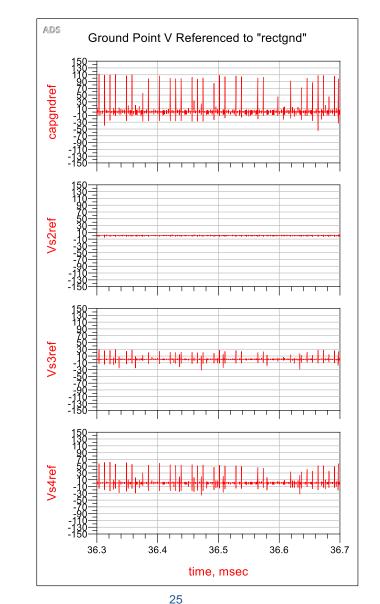

### The Impact on Noise Immunity

#### GAINING INSIGHTS INTO THE DESIGN

- When the grounds of a logic gate contain noise, the noise immunity of the gate decreases.

- The logic gate sees the signal appearing at its input pin with respect to its local ground.

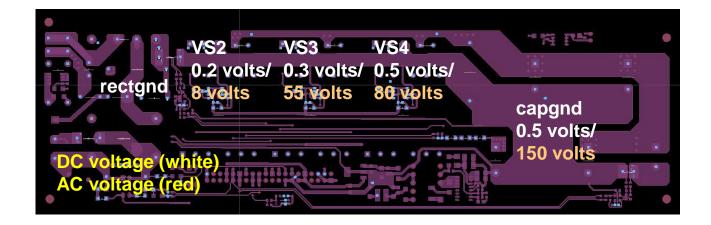

### **Ground Mismatch Example**

#### VOLTAGE VARIANCE ACROSS A GROUND PLANE

Each point on a power plane or trace has:

- IR drop (DC component)

- di/dt (AC component)

- Different amplitude

- Not necessarily coherent

Each point is different!

### **Ground Mismatch Example**

#### EVERYTHING IS RELATIVE!

- It is important to understand the relative voltages around a component.

- Signals going into or out of a device are referenced to the local ground

- Noise levels are different across a ground plane and not necessarily coherent

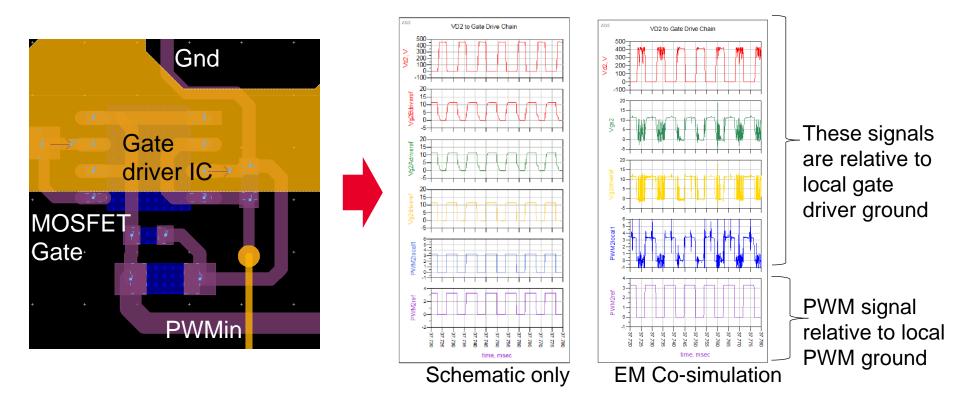

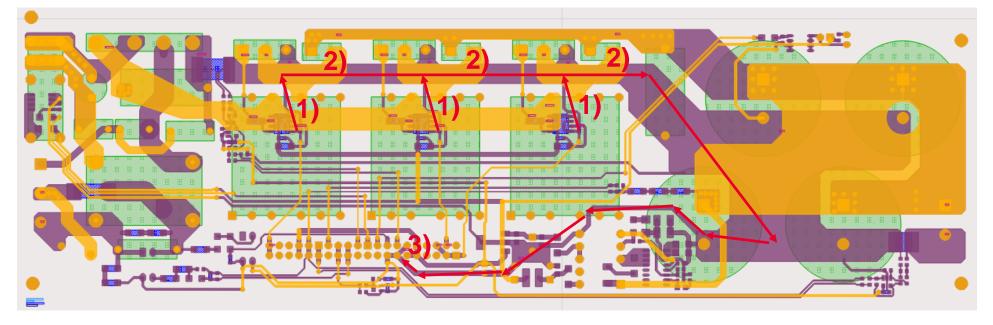

### **Ground Mismatches:**

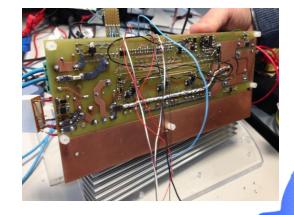

#### EM CO-SIMULATION HELPED WITH DIAGNOSIS

- 1) Gate driver grounds

- 2) Ground plane connecting the power transistors

- 3) PWM ground

Root cause: Excessive ground path from the PWM to the gate drivers, grounds are mismatched along path

### **Ground Mismatch Reduction**

#### PHYSICAL LAYOUT REMEDIES

#### Trace layout:

Reduce IR drop & di/dt by widening traces, shrinking route length. Reduce high current loops

#### **Ground tying:**

Adjust routing to balance ground between critical nodes (V1 & V2)

#### Low ESL capacitors:

Add where large switching transients are generated and between critical components

cap

cap

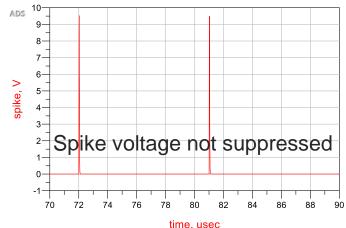

### **Suppressing Voltage Spikes**

#### HIGH VOLTAGE, LOW ESR CAPACITORS

#### Consider a 2.2 uF, 600V poly film low ESR capacitor

- 33 mOhm ESR

- 18 nH lead inductance!

#### **Observations:**

- Higher voltage capacitors have more lead inductance

- Fast switching glitches: rise times are only a few nS!

- Lead inductance may prevent the capacitor from functioning properly

#### ⊗TDK

#### Technical data

| Max. operating temperature<br>Topmax                                                                                                                                                                                            | +125 °C                   |                                                                            |                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Dissipation factor tan 8 (in 10-3)                                                                                                                                                                                              |                           | C <sub>R</sub> ≤ 0.1 µF                                                    | 0.1 µF< C <sub>R</sub>                                                                             |

| at 20 °C (upper limit values)                                                                                                                                                                                                   | at 1 kHz<br>100 kHz       | (.)[])                                                                     | 1.0                                                                                                |

| $\begin{array}{l} \mbox{Insulation resistance $R_{ins}$} \\ \mbox{or time constant $\tau$ = $C_R$ $\cdot$ $R_{ins}$} \\ \mbox{at 20 $^\circ$C, rel. humidity $\leq$ 65\%$} \\ \mbox{(minimum as-delivered values)} \end{array}$ | > 30 000 MΩ<br>> 10 000 s | (C <sub>R</sub> ≤ 0.33 μF)<br>(C <sub>R</sub> > 0.33 μF)                   |                                                                                                    |

| Total self-inductance L<br>(lead length ≈ 3mm)                                                                                                                                                                                  | LS 15 mm<br>LS 22.5 mm    | 10 nH<br>18 nH                                                             |                                                                                                    |

| DC test voltage                                                                                                                                                                                                                 | $1.6 \times V_R$ , 2 s    |                                                                            |                                                                                                    |

| Category voltage $V_C$<br>(continuous operation with $V_{DC}$ or $V_{AC}$ at $f \le 1$ kHz)                                                                                                                                     | T <sub>A</sub> (°C)       | DC voltage derating                                                        | AC voltage derating                                                                                |

|                                                                                                                                                                                                                                 |                           | $V_{\rm C} = V_{\rm R}$ $V_{\rm C} = V_{\rm R} \cdot (165 - T_{\rm A})/80$ | $V_{C,RMS} = V_{RMS}$<br>$V_{C,RMS} = V_{RMS} \cdot (165 - T_A)/80$                                |

| Operating voltage $V_{op}$ for<br>short operating periods<br>$(V_{DC} \text{ or } V_{AC} \text{ at } f \le 1 \text{ kHz})$                                                                                                      | T <sub>A</sub> (°C)       | DC voltage (max. hours)                                                    | AC voltage (max. hours)                                                                            |

|                                                                                                                                                                                                                                 |                           |                                                                            | $V_{op} = 1.0 \cdot V_{C,RMS} (2000 \text{ h})$<br>$V_{op} = 1.0 \cdot V_{C,RMS} (1000 \text{ h})$ |

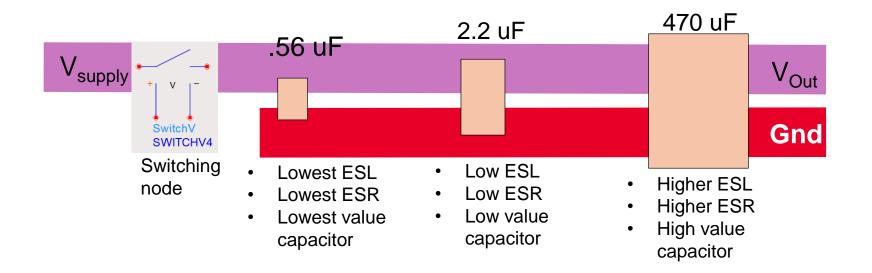

### **Suppressing Voltage Spikes**

#### STAGGERED BYPASS CAPACITORS

#### Low ESL capacitors:

Stagger capacitor types between the switching node and the output with lowest ESL capacitors nearest the switching node

### **Application of HV, Low ESR Capacitors**

#### **BIGGER IS NOT NECESSARILY BETTER**

KEYSIGH1

TECHNOLOGIES

31

# Don't Add Decaps Until the Layout is as Good as it Can Be

### **Troubleshooting Parasitic Effects**

TOOLS, TECHNIQUES, POST PROCESSING

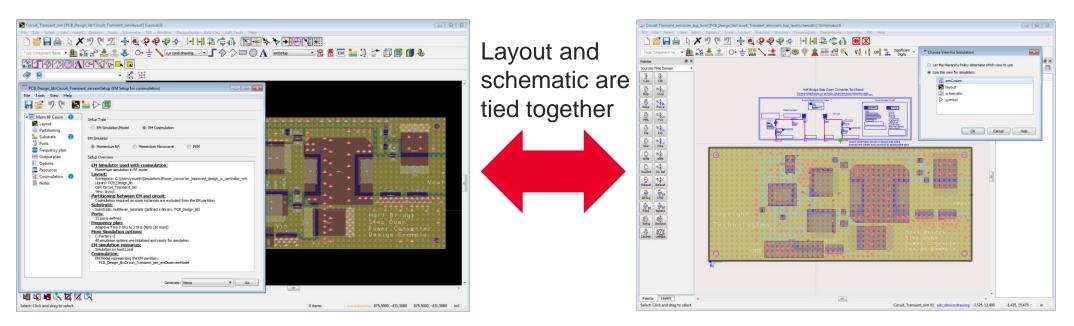

### **Tools – Time for a Demo?**

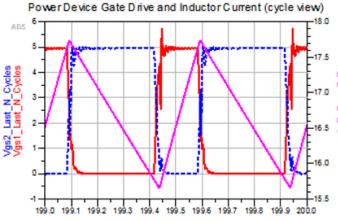

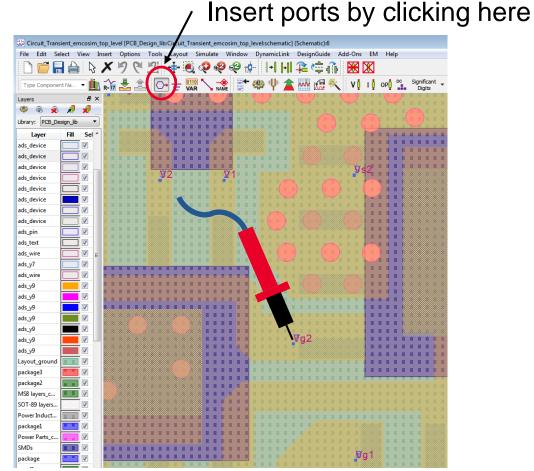

#### USING ADS FOR EM CO-SIMULATION

- EM technologies can be applied to the layout

- Method of Moments EM provides the best balance of speed and accuracy for planar designs

- Simulation can be switched between a schematic and EM cosim view

- EM is utilized <u>with</u> transient or harmonic balance circuit simulation

### **Probing areas of Interest**

#### PROBES ARE EASILY PLACED IN THE LAYOUT

- Probes can be placed at any critical voltage node (like FET gate, drain, gate driver inputs, gnd, etc.)

- Probes can also be placed along a trace plane at different spots to gain di/dt insights

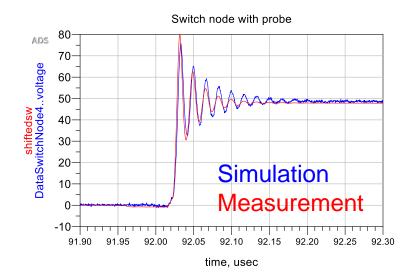

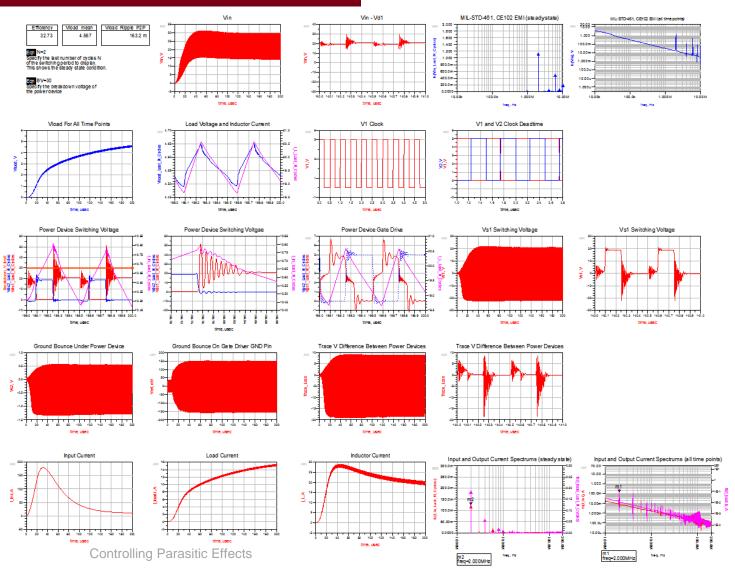

### **Post Processing in ADS**

#### DATA DISPLAY IS A POWERFUL TOOL

Multiple measurements can be conveniently displayed at once.

This can include: switching waveforms, ground bounce, EMI, di/dt trace drop etc.

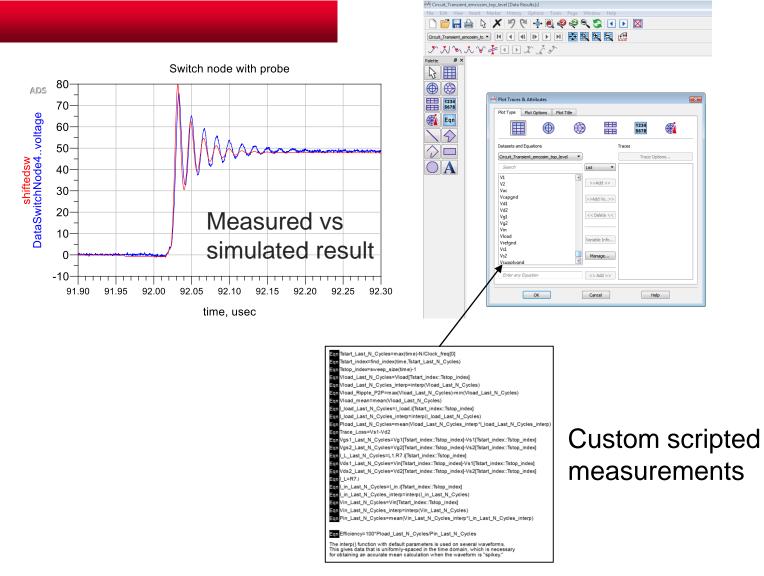

### **Post Processing Flexibility**

#### CUSTOM MEASUREMENTS

- ADS provides flexibility to measure just about anything

- Embedded measurements

- Individual measurement of layout probe points

- Custom scripted

measurements

- Measured vs simulated results

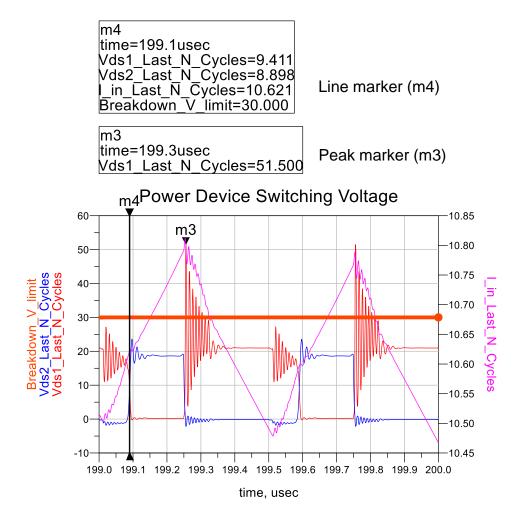

### **Measurement Precision**

#### USING DATA DISPLAY MARKERS

Marker palette

- Markers make it easier to measure data

- Markers are inserted to measure points

of interest

- Markers can be used to measure the period of ringing, rise times, or differential timing

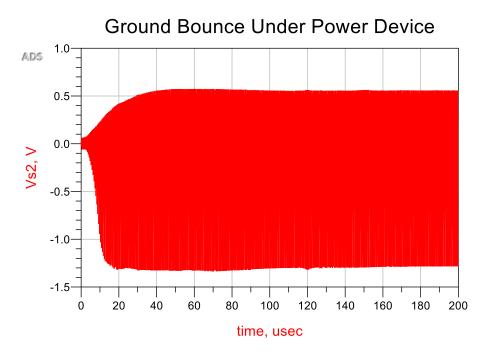

### **Troubleshooting Using ADS**

#### **GROUND BOUNCE EXAMPLES**

Ground bounce reduces converter efficiency, produces common mode noise, and degrades noise immunity.

This performance is good

**KEYSIGH1**

Ground bounce near a voltage reference or gate driver can degrade noise performance.

This performance is good

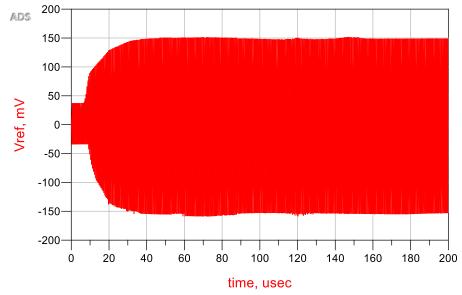

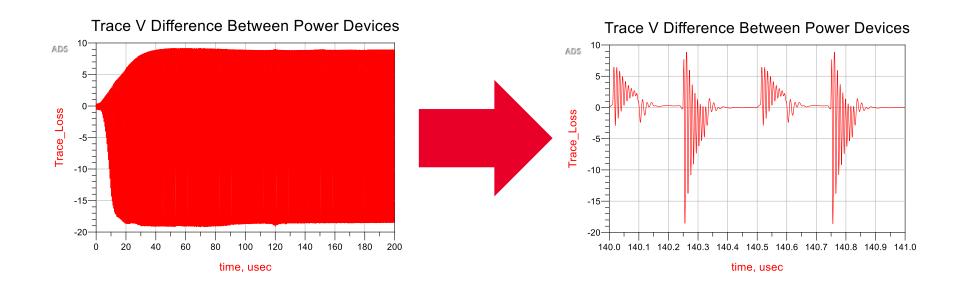

### **Troubleshooting Using ADS**

#### dI/dT EXAMPLE - VOLTAGE DROP ACROSS A TRACE

Probes placed along traces can be subtracted from each other to gain insights

- Where high current loops drive L di/dt effects

- Impact on switching efficiency

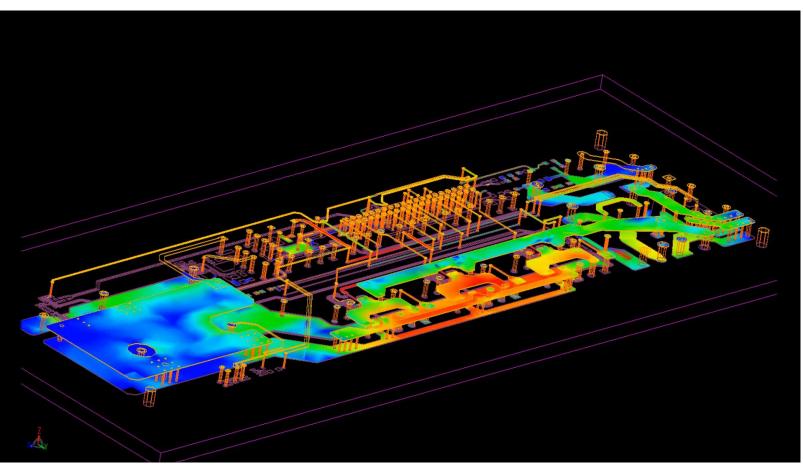

### **Troubleshooting Using ADS**

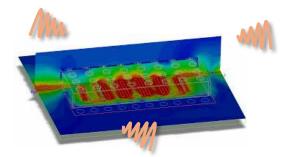

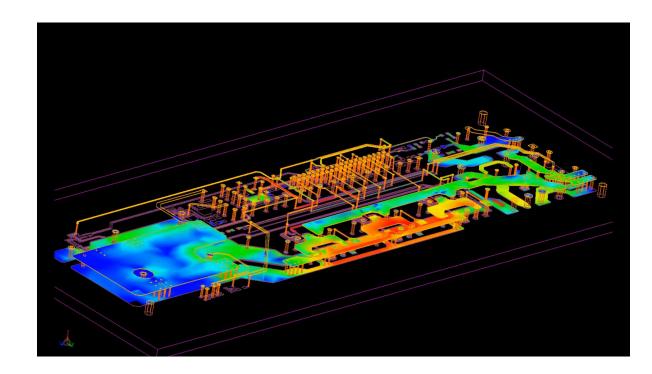

#### EM EXCITATION EXAMPLE

- EM excitation provides current or voltage density to troubleshoot "hot spots"

- Visualization can be manipulated to provide different views

### Conclusions

- Parasitic effects degrade performance and can cause failure

- All physical implementations include parasitics and their impact may not be seen with a schematic-only simulation

- Spiking, noise, ringing, oscillations, false triggering, etc.

- Every ground point on a physical design is different!

- Ground differences reduces noise immunity a reliability concern

- Modern EDA tools and high speed design techniques can be used to verify, troubleshoot, and optimize a design