# PathWave RFIC Design (GoldenGate) 2020

CHEN, Jason

Oct. 2019

Application Engineer

......

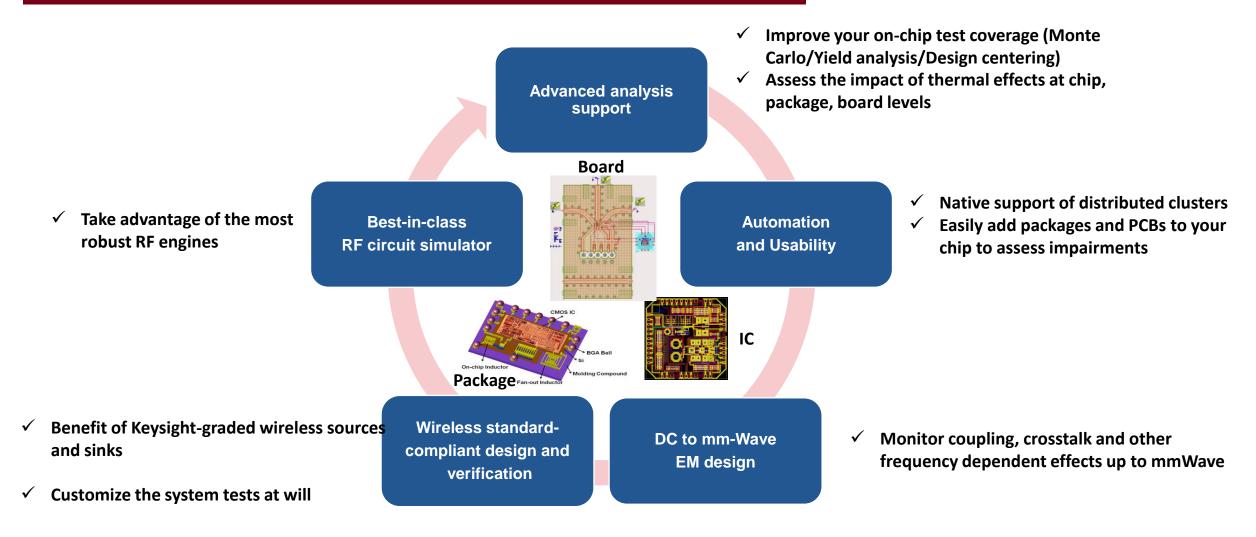

### **Keysight EEsof RFIC solutions**

#### FROM TRANSISTORS TO CONNECTORS

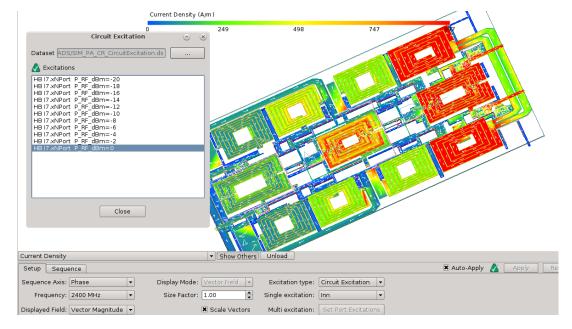

### Analyze your EM circuit under real conditions

- Challenge:

- At high frequencies, coupling is one of the most common problems designers face

- But EM coupling is often analyzed without any non-linear devices and them improper loading

- GoldenGate 2020 now allows interaction with RFPro to look at current densities that correspond to your design under operating conditions

Look at current densities at the harmonic or power you want

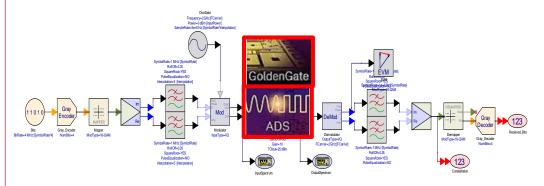

### **Design with modulated signals**

#### DIFFERENT PLATFORMS BUT A COMMON NEED

#### System architecture engineers needs

- Check RF impairments without loss of speed

- Be proactive on the RF impairments with digital processing

- Want to stay inside a system platform

#### **RF designer needs**

- Quickly test their RF IPs on the latest wireless standards

- Do not want to understand fully the standards

- Want to stay inside Cadence Virtuoso or Keysight ADS

- Want to avoid overdesign due to IP3/IP5... approximations

Solution : Bring circuit accuracy inside SystemVue Solution : Bring SystemVue libraries inside Cadence

Same sources, same outputs !

EVM Peak

EVM RMS

IQ Offset (dB20)

Phase Error Peak (°)

Phase Error RMS(°)

28.086

8.676

-51.79

-9.313

2.017

PathWave RFIC Design (GoldenGate) 2020

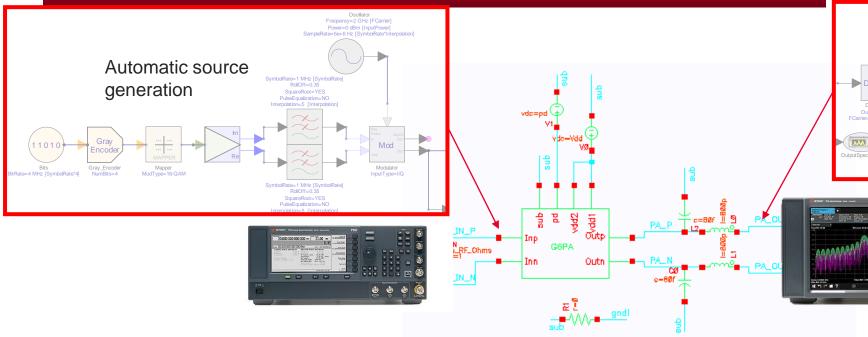

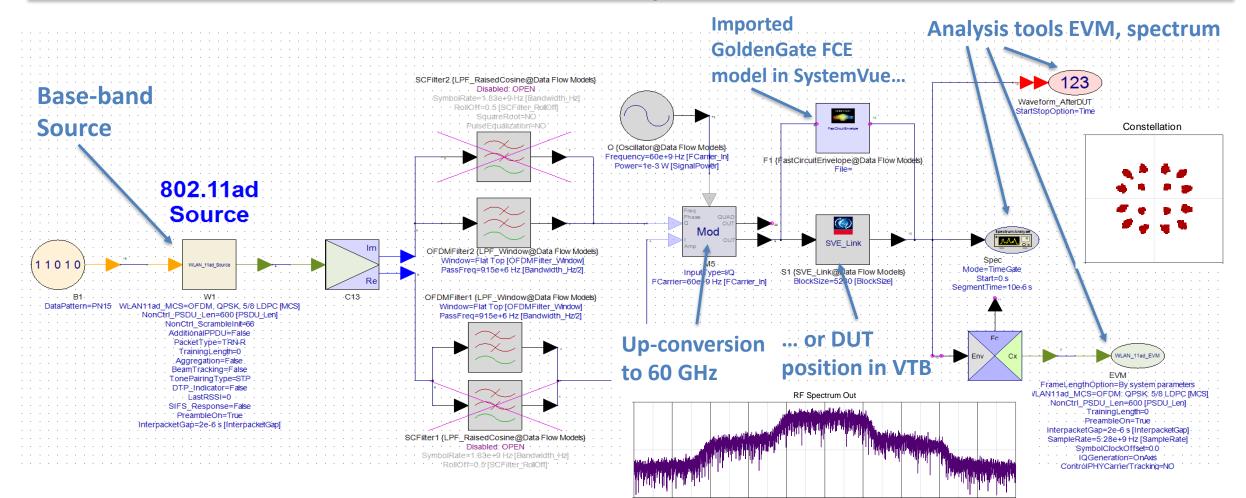

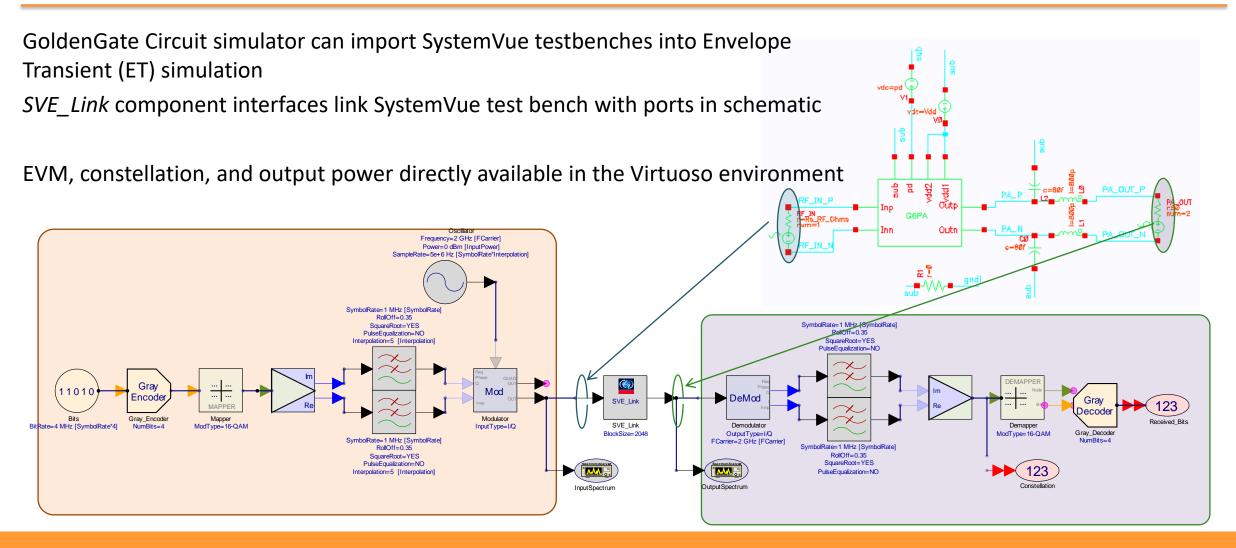

### **RF designers workflow : Virtual Testbenches**

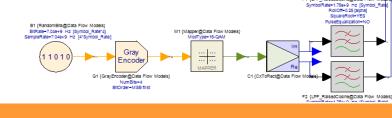

#### BRING SYSTEMVUE INSIDE ADS OR VIRTUOSO

ADS/GoldenGate can use SystemVue Virtual Testbenches (VTB) to automatically

- Generate a waveform compliant with wireless standards

- Demodulate the signal to produce system figures of merits (EVM, CCDF,...)

Keysight Fast Envelope algorithms speed up simulations by orders of magnitude vs. classical Envelope

VTBs boast traceability of the tests used (bandwidth, modulation scheme, source power) than classical methods using files do not offer.

5G NR, Verizon, (U)F-OFDM, FBMC 3GPP / LTE, LTE Advanced 802.11 a/b/n/ac/ad/ah 802.15.3c, 802.15.4, 802.16e Bluetooth (Basic, Enhanced and BLE) GNSS/GPS DVB-x2

Automatic

demodulation

KEYSIGHT TECHNOLOGIES

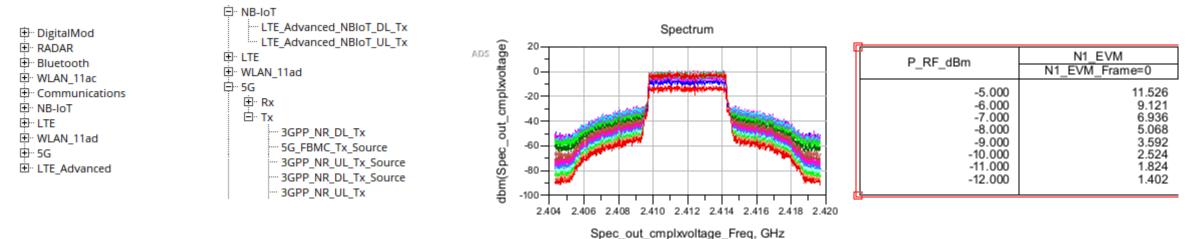

#### Modulated signals update in GoldenGate 2020

#### THE LATEST STANDARDS ARE EMBEDDED !

#### • No need to look for a file or install something else, the modulated signals are one toggle away

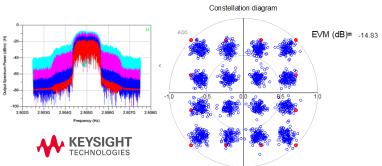

EVM and Output Spectrum of a PA under 5GNR conditions

IP analyses assume a couple of sines. 5GNR waveform [PAPR > 15 dB] is far from being a sine !

### **Distortion EVM**

#### BRING A PNA-X INSIDE VIRTUOSO

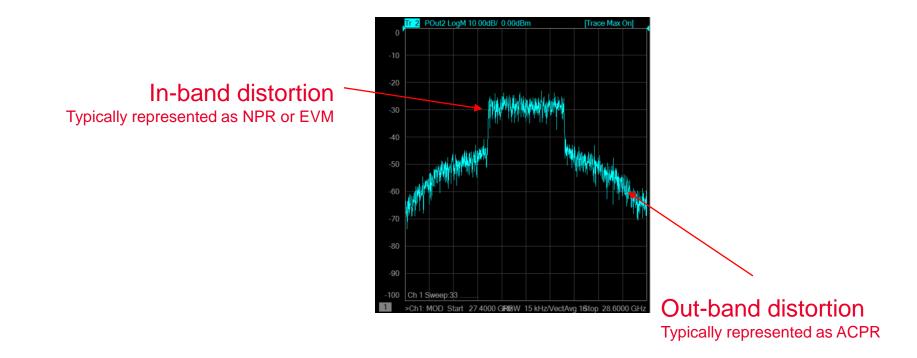

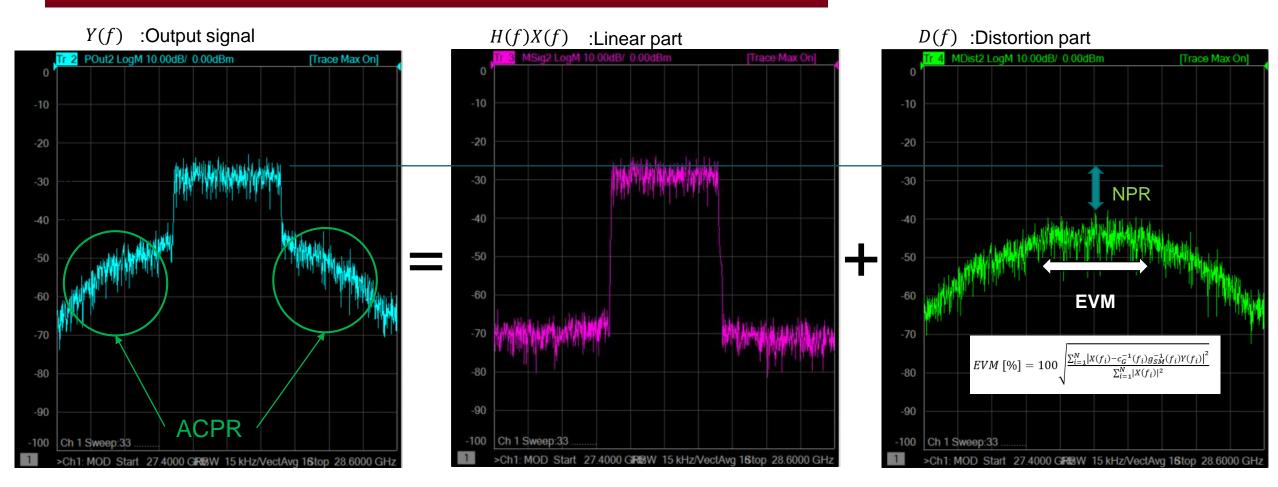

Output Signal Spectrum

- If you have your own IQ files, computing an EVM is a challenge

- What are the bandwidth/numerology/number of subcarriers/...?

- Spectral regrowth (ACPR) does not give all the needed insights

### **Underlying Technology**

#### **COMPUTING FIGURE OF MERITS**

• EVM computed from time domain and frequency domain are mathematically equivalent (Parseval's theorem)

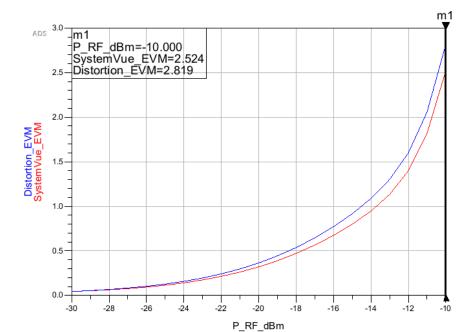

### **Distortion EVM inside GoldenGate**

- Available as a performance (percent or dB) inside GoldenGate

- Allows sweeps, MonteCarlo, LoadPull, integration into ADE-XL or Maestro

- Extended to devices with frequency translation

- Complements VTB reference EVMs

| Dist_EVM_pct              |                      |          | Add             | Ch    |

|---------------------------|----------------------|----------|-----------------|-------|

| distortion_evm_pct("VTB_5 | "PA_OUT",1,0,0,10e6) |          |                 |       |

| In                        | put                  | Input    | Output Output   | Band  |

| SO                        | urce                 | harmonic | source harmonic | width |

5GNR PA EVM SystemVue Distortion Less than 0.3% diff

#### Designing an Award-Winning mmWave RFIC: Experiences and Insights

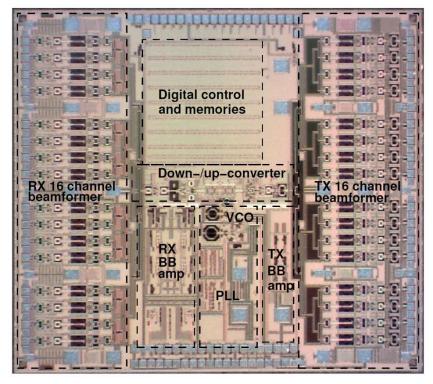

<u>Erik Öjefors</u>, Mikael Andreasson, Torgil Kjellberg, Håkan Berg, Lars Aspemyr, Richard Nilsson, Klas Brink, Robin Dahlbäck, Dapeng Wu, Kristoffer Sjögren and Mats Carlsson

802.11ad 60-GHz RF transceiver chip

# SIVERS

# Outline

- Introduction of Sivers IMA AB

- Application of the 802.11ad standard for fixed-wireless access and backhaul

- Key performance parameters and design challenges

- Overview of the Keysight tools used in the design flow

- SystemVue, GoldenGate, and VTBs

- Chip design and simulation

- Architecture and key circuit blocks, beamformer, LNA, PA and VCO

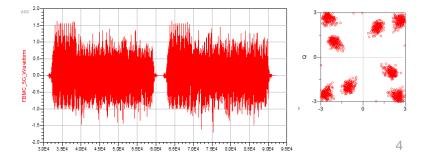

- Modulated signals and EVM performance on transistor level, early feedback to system simulation

- Measurements and comparison to simulations

- Focus on modulated signals and EVM performance

- Link between simulations and measurements

- Conclusion and comparison to state-of-the-art

### Sivers IMA Holding AB in Short

- Sivers IMA delivers key technology for multi-Gbit/s fiber and wireless networks

- HQ in Stockholm, offices in Glasgow and Gothenburg both with sales, R&D and Lab

- 100 employees and 15 consultants

- Listed at Nasdaq First North stock exchange in Stockholm

# SIVERS MA

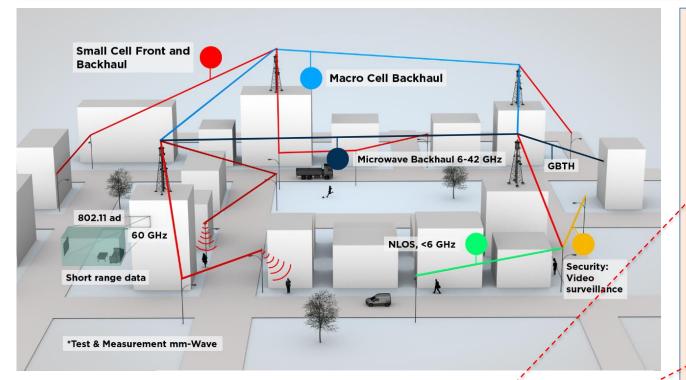

### The Road to Gigabit Speeds Goes Via mmWave

#### **KEY RF COMPETENCE:**

- mmWave

- 802.11ad/ay and 5G

- Phased array antennas

- Beam steering/ Beam forming

- Low phase-noise synthesizers

# Outline

#### • Introduction of Sivers IMA AB

- Application of the 802.11ad standard for fixed-wireless access and backhaul

- Key performance parameters and design challenges

- Overview of the Keysight tools used in the design flow

- SystemVue, GoldenGate, and VTBs

- Chip design and simulation

- Architecture and key circuit blocks, beamformer, LNA, PA and VCO

- Modulated signals and EVM performance on transistor level, early feedback to system simulation

- Measurements and comparison to simulations

- Focus on modulated signals and EVM performance

- Link between simulations and measurements

- Conclusion and comparison to state-of-the-art

### FWA and Backhaul with 60-GHz 802.11ad (WiGig)

Self-organizing mesh networks for 60GHz carrier-grade access points with Gbit speed up to 500m distance based on 802.11ad.

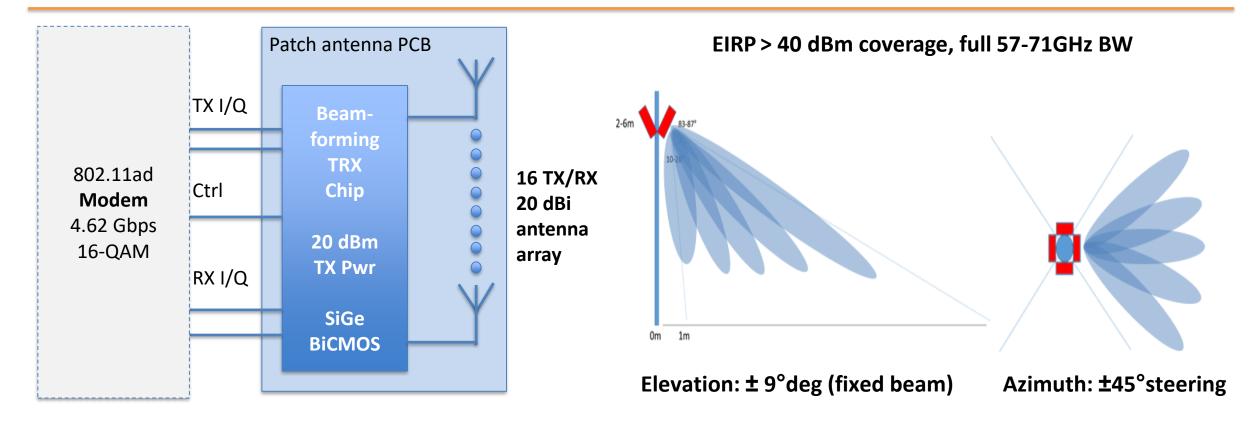

#### Key performance parameters!

- New FCC/ETSI rules drive new radio spec

- 40 dBm EIRP allowed with a low-gain (typ. 20 dBi) antenna, requires

20 dBm TX power

- Frequency range 57-71 GHz

(previously 57-66 GHz), two extra channels

- Half-channel 64/128/256 QAM modulation for dense networks

- Phase noise, < 100 dBc@1MHz</p>

### Our 802.11ad Solution for Infrastructure Equipment

- Challenging system design, baseband 0-1 GHz, severe timing requirements

- Rapid (<35 ns) steering over 64 beams

- Competitive market, demand for first-time right designs

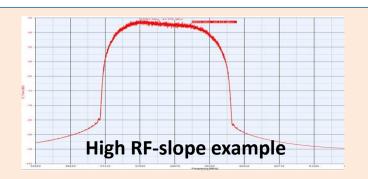

# Design Challenges (i)

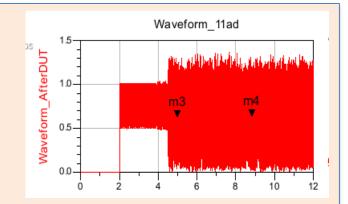

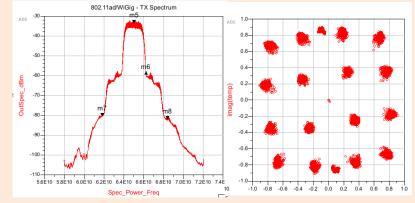

#### Maximizing output power with acceptable EVM and DC power

- Modulations in 802.11ad are quite robust, operation close to P1dB possible

- OIP3 not useful when operating close to close compression!

- Predicting output power using 802.11ad waveform in envelope simulation

- Goal: Maximize output power with TX EVM < -21 dB (802.11ad spec)

- On transistor level in Cadence, check PA load and bias

- EVM partitioning (PA, VCO...) in system simulator

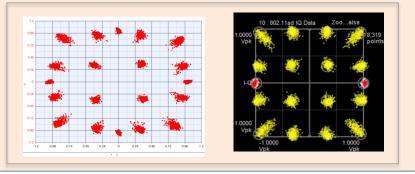

- Get constellation diagrams early in circuit design, great for intuitive understanding

- AM-PM and unsymmetries

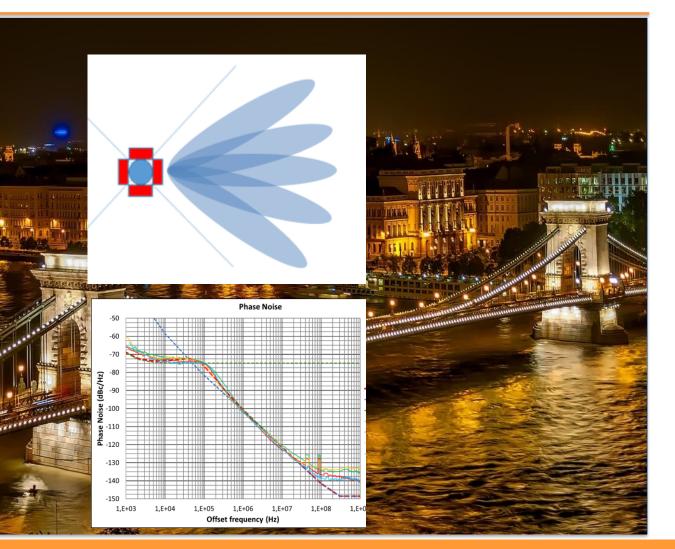

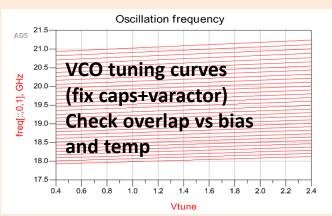

# Design Challenges(ii)

#### Channel width 2 GHz, 57-71 GHz freq. range

- Frequency response not flat in either RF or analog BB

- Need to model EVM degradation and spectrum in system simulator

#### **Phase noise**

SIVERS

- High phase-noise requirements, and a large band

- Two VCO cores and varactor/fix cap topology

- Large simulation matrix requires fast simulator

# High circuit complexity, 16 TX/RX paths and on-chip frequency generation

HB simulator speed and ability to handle large designs

# Outline

- Introduction of Sivers IMA AB

- Application of the 802.11ad standard for fixed-wireless access and backhaul

- Key performance parameters and design challenges

- Overview of the Keysight tools used in the design flow

- SystemVue, GoldenGate, and VTBs

- Chip design and simulation

- Architecture and key circuit blocks, beamformer, LNA, PA and VCO

- Modulated signals and EVM performance on transistor level, early feedback to system simulation

- Measurements and comparison to simulations

- Focus on modulated signals and EVM performance

- Link between simulations and measurements

- Conclusion and comparison to state-of-the-art

### An 802.11ad Testbench for SystemVue and GoldenGate

Erik Öjefors

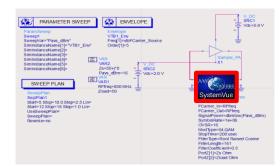

# Virtual Test Bench - Using VTBs in Cadence Virtuoso

### SIVERSIMA

Erik Öjefors

# VTB Setup in Cadence Schematic and ADE/Explorer

| These bursts for VIB Surves (fugetise Voltage Surves)       Have Derride Surves     +Pesitive Nois       Have Derride Surves     +Pesitive Nois       Mase Derride Surves     +Pesitive Nois       Answe Frets - VIB Surves (Calleted signals - Voltage probes)       Have Derride Surves     +Pesitive Nois       Have Derride Surves     +Pesitive Nois       Provesters     Derrection       Provesters     0       Strik     - VIB Surves (Calleted signals - Voltage probes)       Have Derride Surves     +Perseters       Provesters     Derrection       Provesters     0       Signal Paret     0       Carright Fract     0       Lonignoffrat     0       Carright Signal Surves     Need Kern Set Menakt       Carright Signal Surves     0       Carright Signal Surves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Analyses<br>Type En<br>1 ET<br>2 SSNA<br>3 CR<br>4 DC                   | able Arguments                                                                                                                        |                                                                         | <ul> <li>GoldenGate Simulator settings in Analog Environment</li> <li>Choosing Envelope simulation</li> <li>Variables that can changed in the SystemVue</li> <li>Defining in/out ports in schematic window</li> </ul> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Perseters connection Perseters ton<br>Perseters connection Perseters to<br>Perseters connection Perseters ton<br>Perseters connection Perseters ton<br>Dorts connection Perseters ton<br>Perseters connection Perseters ton<br>Perseters connection Perseters to<br>Connection (rad) O connection (rad                                                                                                                                                                                                 | Name Override So<br>Source V /PORTO<br>Output Ports - VIB S             | urce *Positive Node *Negative Node *Series Res<br>Select /net034 Gelect /gnd! Select ZL<br>Sinks (Collected signals - Voltage probes) | 1.0                                                                     |                                                                                                                                                                                                                       |

| MirrorSignal N0<br>GainInbalance 0<br>PhaseIabalance (rad) 0<br>L_DriginOffset 0<br>Q_DriginOffset 0<br>L_DriginOffset 0<br>Q_DriginOffset 0<br>L_DriginOffset 0<br>L_Drigin | Parameters Con<br>FCarrier_In (Hz)<br>FCarrier_Out (Hz)                 | nection         Pan           6000000000         elect Var           60000000000         elect Var                                    | S.t Default                                                             |                                                                                                                                                                                                                       |

| IU_Rotation (rad)     0     elect Var., Set Default       OversampleRatio     3       InterpacketGap (sec)     2e-06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MirrorSignal<br>GainImbalance<br>PhaseImbalance (rad)<br>I_OriginOffset | NO<br>O<br>O<br>elect Var.,<br>O<br>elect Var.,<br>O<br>elect Var.,                                                                   | Set Default<br>Set Default<br>Set Default<br>Set Default                | RF_IN<br>SI-RS_RF_Ohms<br>G6PA                                                                                                                                                                                        |

| MCS     SC. P1/2-QAM16, 3/4 LDPC     Set Default       PSDU_Len     2000     Set Default       TimeStop (sec)     Be-06     elect. Var., Set Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OversampleRatio<br>InterpacketGap (sec)<br>MCS<br>PSDU_Len              | 0 elect Var.)<br>3<br>2e-06 elect Var.)<br>SC, P1/2-QRM16, 3/4 LDPC •                                                                 | Set Default<br>Set Default<br>Set Default<br>Set Default<br>Set Default |                                                                                                                                                                                                                       |

# Outline

- Introduction of Sivers IMA AB

- Application of the 802.11ad standard for fixed-wireless access and backhaul

- Key performance parameters and design challenges

- Overview of the Keysight tools used in the design flow

- SystemVue, GoldenGate, VTBs, ADS Momentum for custom passives

- Chip design and simulation

- Architecture and key circuit blocks, beamformer, LNA, PA and VCO

- Modulated signals and EVM performance on transistor level, early feedback to system simulation

- Measurements and comparison to simulations

- Focus on modulated signals and EVM performance

- Link between simulations and measurements

- Conclusion and comparison to state-of-the-art

# **Chip Evaluation Results**

- TX compression and EVM measurements

- RX NF and EVM measuremens

- Synthesizer phase-noise compared to simulations

- Beam-steering results with a PCB patch-array antenna

- Over-the-Air (OTA) full system tests up to 10 Gbit/s

# Full TX-RX System Analysis using SystemVue and FCEs

- VCO PN & TX PA QUAD Error After PA After LNA P=9.7 dBm rms EVM -24.3 dB EVM -24.9 dB ator@Data Fig 2 (Oscillator@Data Flow requency=60e9 H Power=10 dBm F6 (FastCircuitEnvelope@Data Fi cillator@Data Fl Frequency=60e9 Hz Power=10 dBm post\_LNA {EVM\_Env@Data Flow Mod Path 123 123 mplifier@Data Flow LNA utterworth@Data Flow Model loss Gain=11 NA\_sink {Sink@Data Flow M NoiseFloure=45 -----2 (Modulator@Data Flow lifer@Data Flow nolifier@Data Flow Model Demodulator@Data Flow dulator@Data Flow Model InputType=I/Q FCarrier=60e9 H InputType=I/Q FCarrier=60e9 H (FastCircultEnvelope@Data Flov OutputType=I/C FCarrier=60e9 F Gain-10 kmnSensitivity=0.3 VolseFigure=10 GCTvpe=TOI AmpSensitivity-Gainimbalance-0.5 (123) sink (Sink@Data Flow Mo out {EVM\_Env@Data Flow Models Final EVM -24.3 dB Before PA 1 (LPF RaisedCosine@Data Flow de=1 75e+9 P=0.3 dBm rms EVM -33.2 dB

- Total effect of IQ imbalance, PN, PA nonlinearity, LNA NF, Filtering

- EVM degradation can be observed along the signal path

# Outline

- Introduction of Sivers IMA AB

- Application of the 802.11ad standard for fixed-wireless access and backhaul

- Key performance parameters and design challenges

- Overview of the Keysight tools used in the design flow

- SystemVue, GoldenGate, VTBs, ADS Momentum for custom passives

- Chip design and simulation

- Architecture and key circuit blocks, beamformer, LNA, PA and VCO

- Modulated signals and EVM performance on transistor level, early feedback to system simulation

- Measurements and comparison to simulations

- Focus on modulated signals and EVM performance

- Link between simulations and measurements

- Conclusion and comparison to state-of-the-art

### Beamsteering 60GHz TRX Comparison

| Reference                                    | Technology/<br>Configuration  | Oper. freq.<br>[GHz] | Combined Output<br>Power/P1dB [dBm]                              | Phase noise<br>[dBc@1MHz] | DC power<br>[W] |

|----------------------------------------------|-------------------------------|----------------------|------------------------------------------------------------------|---------------------------|-----------------|

| Emami <i>et al</i> , ISSCC<br>2011 (Sibeam)  | 65nm CMOS<br>32RX+8TX         | 59.4-<br>63.72       | 28 dBm EIRP                                                      | -96                       | 0.9-2.2         |

| Boers <i>et al</i> , JSSC<br>2014 (Broadcom) | 40nm CMOS<br>16RX+16TX        | 57-66                | 24 dBm EIRP                                                      | -                         | 0.96-1.2        |

| Valdes-Garcia et al,<br>JSSC 2010 (IBM)      | 130nm SiGe<br>16 TX (sep. RX) | 51-65                | 21-25.5                                                          | -90 to -87                | 3.8-6.4         |

| This work                                    | 130nm SiGe<br>16RX+16TX       | 57-71                | 22 (57-66 GHz) (<br>20 (66-71 GHz)<br>>40 dBm EIRP (20 dBi ant.) | -101                      | 2.6-5           |

| <b>SIVERS</b>                                |                               | (                    | Erik Öjefors                                                     |                           | 27              |

# Conclusion

- A 60-GHz 16-ch beam-steering transceiver demonstrated capable of +40dBm EIRP when used with a 20 dBi PCB antenna array

- The frequency range 57-71 GHz covered with wide-band matching and VCO design techniques

- ADS Momentum used for custom inductors/transformers and full sub-circuit passive modelling

- Phase-noise performance of -101 dBc@ 1 MHz supports 256QAM modulation across OTA link

- GoldenGate and Virtual Test Benches (VTBs) used in circuit design on transistor level. Delivers EVM and spectrum estimations with 802.11ad waveforms in the Cadence environment

- Fast Circuit Envelope (FCE) models exported to SystemVue to refine system simulation

- GoldenGate speed and convergence supported top level simulations of full TX/RX path

# SIVERS MA